BÖLÜM 9

DARLINGTON ÇİFTİ ve PNP/NPN TAMAMLAYICI ÇİFT DEVRELERİ

Amaç: Darlington devresinin incelenmesi ve PNP/NPN tamamlayıcı çift devresi ile çeşitli

ölçümlerin gerçekleştirilmesi

BİLGİ

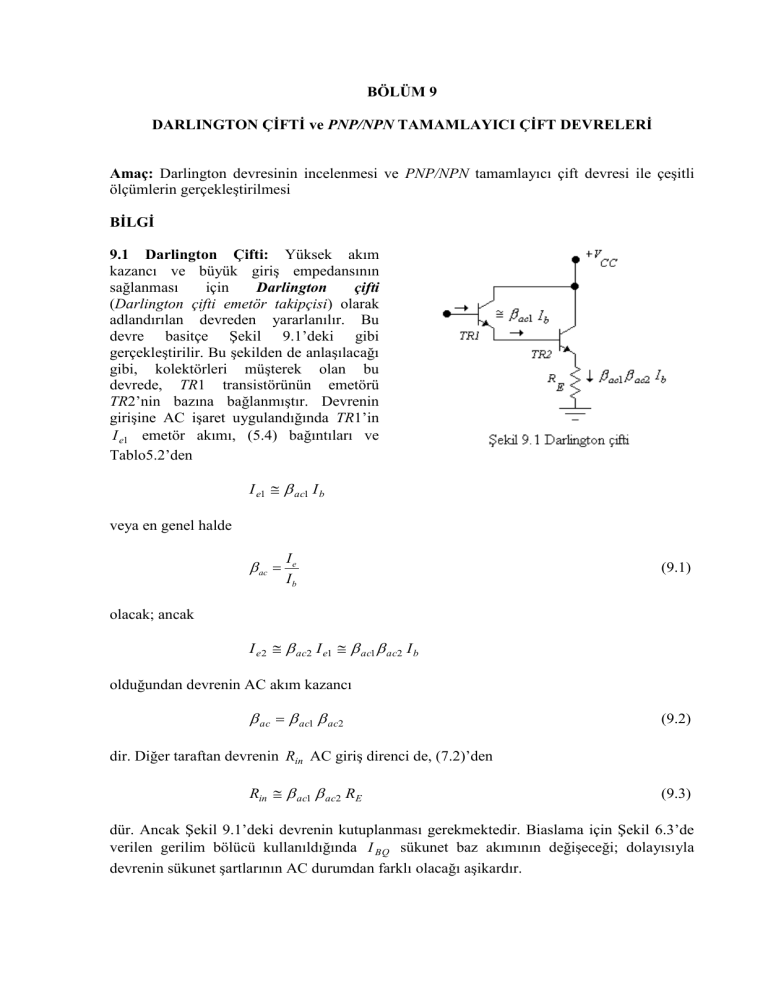

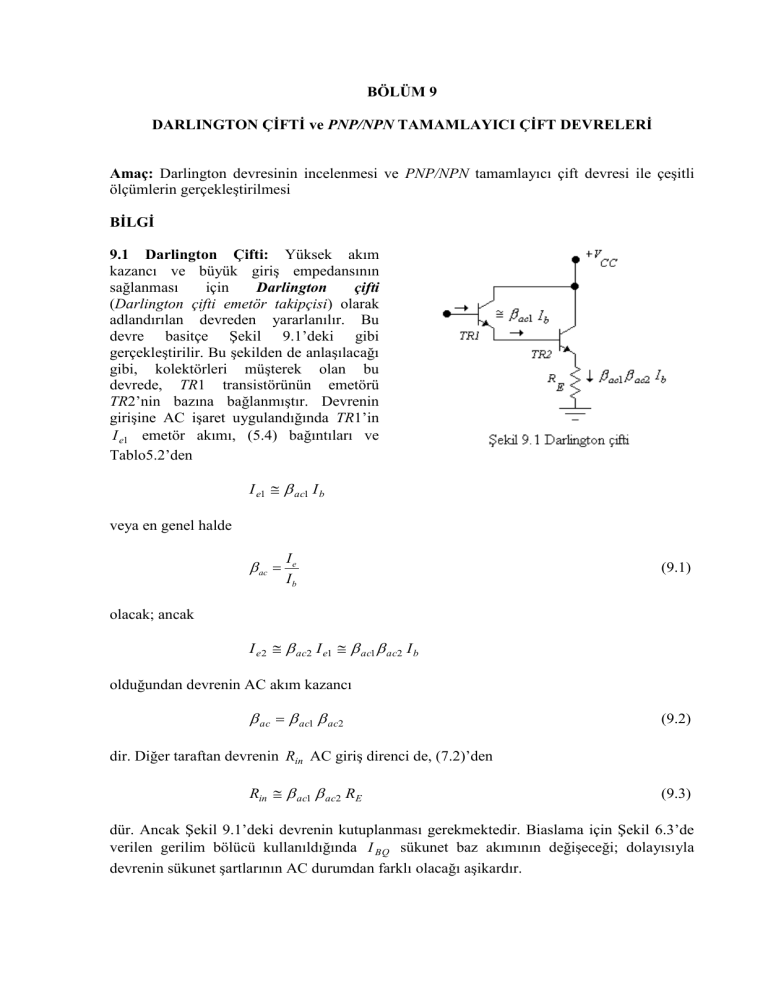

9.1 Darlington Çifti: Yüksek akım

kazancı ve büyük giriş empedansının

sağlanması

için

Darlington

çifti

(Darlington çifti emetör takipçisi) olarak

adlandırılan devreden yararlanılır. Bu

devre basitçe Şekil 9.1’deki gibi

gerçekleştirilir. Bu şekilden de anlaşılacağı

gibi, kolektörleri müşterek olan bu

devrede, TR1 transistörünün emetörü

TR2’nin bazına bağlanmıştır. Devrenin

girişine AC işaret uygulandığında TR1’in

I e1 emetör akımı, (5.4) bağıntıları ve

Tablo5.2’den

I e1 ac1 I b

veya en genel halde

ac

Ie

Ib

(9.1)

olacak; ancak

I e 2 ac2 I e1 ac1 ac2 I b

olduğundan devrenin AC akım kazancı

ac ac1 ac2

(9.2)

dir. Diğer taraftan devrenin Rin AC giriş direnci de, (7.2)’den

Rin ac1 ac2 RE

(9.3)

dür. Ancak Şekil 9.1’deki devrenin kutuplanması gerekmektedir. Biaslama için Şekil 6.3’de

verilen gerilim bölücü kullanıldığında I BQ sükunet baz akımının değişeceği; dolayısıyla

devrenin sükunet şartlarının AC durumdan farklı olacağı aşikardır.

Devrenin iki npn transistörünün şekildeki gibi bağlanmaları Darlington transistörü olarak

anılabilecek tek bir transistör gibi düşünülebilir. Bu takdirde Şekil 9.1’deki devrenin emetör

takipçisi olarak davranacağı kolayca anlaşılabilir.

9.2 PNP/NPN Tamamlayıcı Çift Devresi:

Bilindiği gibi npn transistör, bazı

emetörüne

göre pozitif olduğunda

iletimdedir. Buna karşılık pnp transistör

baz emetöre göre negatif ise iletimdedir.

Dolayısıyla bu iki transistörün ortak

emetörlü (“emetör takipçisi”) aynı bir

devrede Şekil 9.2’deki gibi, simetrik olarak

kullanılmalarıyla

devrenin

girişine

uygulanan

işaretin

genliğine

bağlı

olmaksızın (pozitif veya negatif) daima bir

çıkış elde edilebilir. Böyle bir devre

pnp/npn tamamlayıcı çift olarak anılır.

Şekil 9.3’deki devrede girişe uygulanan

Vin işaretinin pozitif alternansında TR1

transistörü iletimde olacak, buna karşılık

negatif alternansta devrenin Vout çıkış

gerilimi iletimde olan TR2 transistörü ile

sağlanacaktır.

Ancak

transistörlerin

iletimde olabilmeleri için giriş geriliminin

belirli bir VBE gerilimine eşit veya daha

büyük alması gerektiğinden; çıkışta Şekil

9.3’de de görüldüğü gibi, pozitif ve negatif

alternans arasında bir zaman bozulması

(“crossover distortion”) oluşur. Oluşan bu

bozulma, sadece giriş işaretinin olmaması

.

durumunda iki transistörün kesimde

olmalarıyla önlenebilir.

Bu ise transistörlerin gerilim bölücü devrelerle biaslanmaları ile bir ölçüde sağlanabilir.

Ancak VBE ’nin sıcaklıkla değişimi devrenin sabit bir gerilimde biaslanmasını zorlaştırır. Bu

da gerilim bölücünün bir direncinin yerine diyotlar (veya transistörler) kullanılarak

önlenebilir.

DENEY

A) Darlington çiftinin DC Karakteristiklerinin Belirlenmesi:

1)Digiac

3000

Semiconductors-2.2

modülünün 1 nolu düzeni yardımıyla Şekil

9.4’deki

Darlington

çifti

devresi

gerçekleştirilir.

2)TR1 transistörüne baz akımı sağlayan,

R1 ve R2 dirençlerinin oluşturduğu gerilim

bölücüdeki V pot , TR1’in ve TR2’nin VE1

ve VE 2 emetör gerilimleri ( VE1 VB2 )

sırasıyla DC voltmetre olarak kullanılan

DM ile ölçülür, sonuçlar Tablo 9.1’e

işlenir.

Tablo 9.1

V pot V

VE1 V

VE2 V

VR3 mV

3)TR1’in bazındaki 100K’lık R3 direncindeki gerilim düşmesi de ölçülerek, sonuç Tablo 9.1’e

geçirilir.

4)Bu değerlerden yararlanılarak TR1 ve TR2’nin VBE1 ve VBE2 baz-emetör gerilimleri

(TR1’inkine dikkat edilerek) hesaplanır, sonuçlar Tablo 9.2’ye geçirilir.

5)Ölçülen VR 3 gerilimi ile Ohm kanunundan yararlanılarak TR1’in I B1 baz akımı hesaplanır;

VB1 baz gerilimi DM ile ölçülerek, sonuçlar Tablo 9.2’ye işlenir. VB1 ölçümünün doğruluğu

ve nedeni araştırılır.

Tablo 9.2

VBE1 V VBE2 V

I B1 A

VB1 V Rin M

6)Tablo 9.1 ve 9.2’deki değerlerden, devre giriş direnci kavramı hatırlanarak bir Darlington

çifti devresinin Rin (DC) giriş empedansı ( Rin Vin / I B1 ) hesaplanır, sonuç Tablo 9.2’ye

işlenir.

7)DC ampermetre olarak kullanılan DM devrenin uygun kısımlarına bağlanarak, sırasıyla TR1

ve TR2’nin I E1 ve I E 2 emetör akımları ( I E1 I B 2 ) ölçülür, sonuçlar Tablo 9.3’e işlenir. Bu

tablodaki I B1 akımı Tablo 9.2’de hesaplanan değerdir.

Tablo 9.3

I B1 nA

I E1 A

1

I B 2 A

I E2 mA

2

1 2

8)Bu değerlerden, (9.1) bağıntısı yardımıyla TR1 ve TR2’nin 1 ve 2 akım kazançları

hesaplanır. Tüm devrenin akım kazancı ise devrenin çıkış ve giriş akımlarının oranı

( I E 2 / I B1 ) olarak bulunur, sonuçlar Tablo 9.3’e geçirilir. akım kazancı kat kazançlarının

1 2 çarpımıyla karşılaştırılır.

9)Şekil 9.4’deki devrede çıkış gerilimi, başka bir deyişle TR2 transistörünün R4 emetör

direnci üzerindeki Vout gerilim düşmesi DM ile ölçülür. Hafifçe nemlendirilmiş parmaklarla

önce TR1’in bazı ile VCC gerilimine, sonra baz ile toprak hattına değdirilir. Bu durumlarda

V1 ve V2 çıkış gerilimleri ölçülür. Sonuçlar Tablo 9.4’e işlenir ve yorumlanır.

Tablo 9.4

Vout V

V1 V

B)Darlington Çiftinin AC İşaret Girişi ile Çalışması:

1)Şekil 9.4’deki devrede bazı değişiklikler

yapılarak

Şekil

9.5’deki

devre

gerçekleştirilir.

2)SG ile devreye uygulanan sinüs

geriliminin frekansı 1kHz’e ve çıkış genliği

minimum seviyeye ayarlanır.

3)SG’nin ile uygulanan sinüs geriliminin

genliği arttırılarak osiloskopla gözlenen

devrenin çıkış geriliminin bozulması

(distorsiyon) sağlanır. Sonra genlik

azaltılarak çıkışta bozulma olmadan elde

edilen Vout çıkış gerilimi ile Vin giriş

geriliminin p-p değerleri ölçülür, sonuçlar

Tablo 9.5’e geçirilir.

V2 V

Tablo 9.5

Vin V

Vout V

p p

p p

4)Osiloskopta gözlenen Vin ve Vout gerilim şekilleri çizilir.

5)Bu eğrilerden veya osiloskopta gözlenen şekillerden giriş ve çıkış işaretleri arasındaki faz

farkı belirlenir, sonuç Tablo 9.5’e işlenir.

6)AC voltmetre olarak kullanılan DM ile devrenin giriş gerilimi ve R3 direnci uçları

arasındaki gerilim düşmesi ölçülür, sonuçlar Tablo 9.6’ya geçirilir. Ölçülen bu giriş gerilimi

ile Tablo 9.5’deki Vin gerilimi karşılaştırılır.

Tablo 9.6

Vin V

VR3 mV

Ib1 A

Rin AC M Rin,hesap M

7)Ölçülen VR 3 değerinden devrenin I b1 giriş akımı hesaplanır. Bu değerle de devrenin Rin

AC giriş empedansı belirlenir, sonuçlar Tablo 9.6’ya işlenir.

8)AC ampermetre olarak kullanılan DM devrenin uygun yerlerine bağlanarak TR1 ve TR2’nin

I e1 ( I e1 I b 2 ) ve I e 2 emetör akımları ölçülür, sonuçlar Tablo 9.7’ye geçirilir. Bu tablodaki

I B1 akımı Tablo 9.6’da hesaplanan değerdir.

Tablo 9.7

I b1 nA

I e1 A

1

I b 2 A

I e2 mA

2

hesap

9)Bu değerlerden (9.1) bağıntısı yardımıyla 1 ve 2 akım kazançları hesaplanır. Devrenin

akım kazancı da hesaplanarak, sonuçlar Tablo 9.7’ye işlenir.

10)Tablo 9.7’deki 1 ve 2 değerlerinden (9.2) bağıntısı yardımıyla devrenin hesap akım

kazancı hesaplanır, sonuç Tablo 9.7’ye geçirilir. Bulunan bu sonuç tablodaki değeri ile

karşılaştırılır.

11)Tablo 9.7’deki 1 ve 2 ile RE R4 1K emetör direnci değerlerinden (9.3) bağıntısı

yardımıyla devrenin Rhesap AC giriş empedansı hesaplanır, sonuç Tablo 9.6’ya geçirilir.

Bulunan bu sonuç tablodaki Rin AC değeri ile karşılaştırılır.

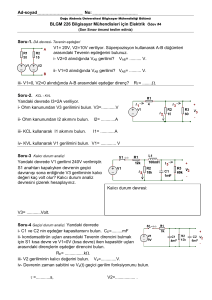

B)PNP/NPN Tamamlayıcı Çift Devresine DC Gerilim Uygulanması:

1)

Digiac

3000

Semiconductors-2

modülünün 2 nolu düzeni yardımıyla Şekil

9.6’da verilen devre gerçekleştirilir.

2)DC voltmetre olarak kullanılan DM ile

TR3 ve TR4 transistörlerinin VB 3 , VB 4 baz,

VE 3 , VE 4 emetör ve VCE 3 , VCE 4 kolektör

gerilimleri ( VCE 3 ,VCE 4 devrenin besleme

gerilimi) ölçülür. Ayrıca devrenin Vin giriş

ve Vout çıkış gerilimleri de ölçülerek

sonuçlar Tablo 9.8’e işlenir. Bu Vin ve

Vout gerilimleri arasındaki fark açıklanır.

3)Devreye giriş gerilimi uygulanmak üzere

5K’lık VR1 potansiyometresi, A ve B

noktaları birleştirilerek bağlanır. Ayrıca C

ve D noktaları birleştirilerek 100 ’luk R9

yük direnci ilave edilir.

Tablo 9.8

VB3 V Vin mV VB 4 V

VC 3 V

VE 3 V

Vout mV

VE 4 V

VC 4 V

4)VR1 potansiyometresi yardımıyla Vin giriş gerilimi, +12V’dan –12V’a birer volt gerilim

aralıkları ile değiştirilerek Vout çıkış gerilimleri DM ile ölçülür, sonuçlar Tablo 9.9’a geçirilir.

Tablo 9.9

Vin V

Vout V Vin V

Vout V

Vin V

Vout V Vin V Vout V Vin V Vout V

+12

+7

+2

-3

-8

+11

+6

+1

-4

-9

+10

+5

0

-5

-10

+9

+4

-1

-6

-11

+8

+3

-2

-7

-12

5)Bu değerlerden devrenin transfer karakteristiği ( Vout f Vin ) çizilir ve yorumlanır.

D)PNP/NPN Tamamlayıcı Çiftinin AC İşaretle Sürülmesi:

1)Şekil 9.6’daki devrede bazı değişiklikler

yapılarak

Şekil

9.7’deki

devre

gerçekleştirilir.

2)SG ile devreye uygulanan sinüs işaretinin

frekansı 1kHz ve çıkış genliği minimum

seviyeye ayarlanır.

3)SG’nin çıkış genliği maksimum seviyeye

getirilerek devrenin giriş ile çıkış

gerilimleri gözlenir ve yorumlanır.

4)Devreye, C ve D noktaları birleştirilerek

R9 yük direnci ilave edilir. Osiloskopla

gözlenen çıkış gerilimi çizilir.

5)SG’nin çıkış genliği ayarlanarak giriş

geriliminin tepeden tepeye 4V olması

sağlanır. Transistörlerin biaslanmalarını

sağlayan diyotlar kısa devre edilerek

devreden çıkarılır.

6)Devrenin giriş ve çıkışında osiloskopla gözlenen gerilimler çizilir.

7)Bu eğrilerden giriş ve çıkış arasındaki zaman bozulması belirlenir.

SORULAR

1)Bir Darlington çifti devresinde aşağıdaki değerler ölçülmüşse her bir transistörün ve

devrenin akım kazanç değerlerini bulunuz. Bu devrenin çıkış (emetör) direnci 120 ise giriş

empedansı nedir?

Baz akımı

Emetör akımı

TR1

96nA

21 A

TR2

21 A

6mA

2)İki Darlington çifti 10V’luk tek bir gerilim kaynağından beslenmektedir. Devrelerin çıkış

(emetör) sükunet gerilimleri 4,6V ve 5,9V ise, distorsiyonsuz maksimum çıkış gerilimlerinin

p-p değerleri nedir?

3)PNP/NPN tamamlayıcı çift devresindeki transistörler nasıl bağlanmışlardır? Bu devre hangi

işlevi sağlar?

4)Böyle bir devrenin giriş ve çıkış işaretleri arasında neden bir zaman farkı veya zaman

bozulması oluşur?