BÖLÜM 7

ÇEŞİTLİ YÜKSELTEÇLER

Amaç: Ortak kolektörlü amplifikatör, PNP ortak emetörlü yükselteç ve iki katlı yükselteç

devrelerinin incelenmesi.

BİLGİ

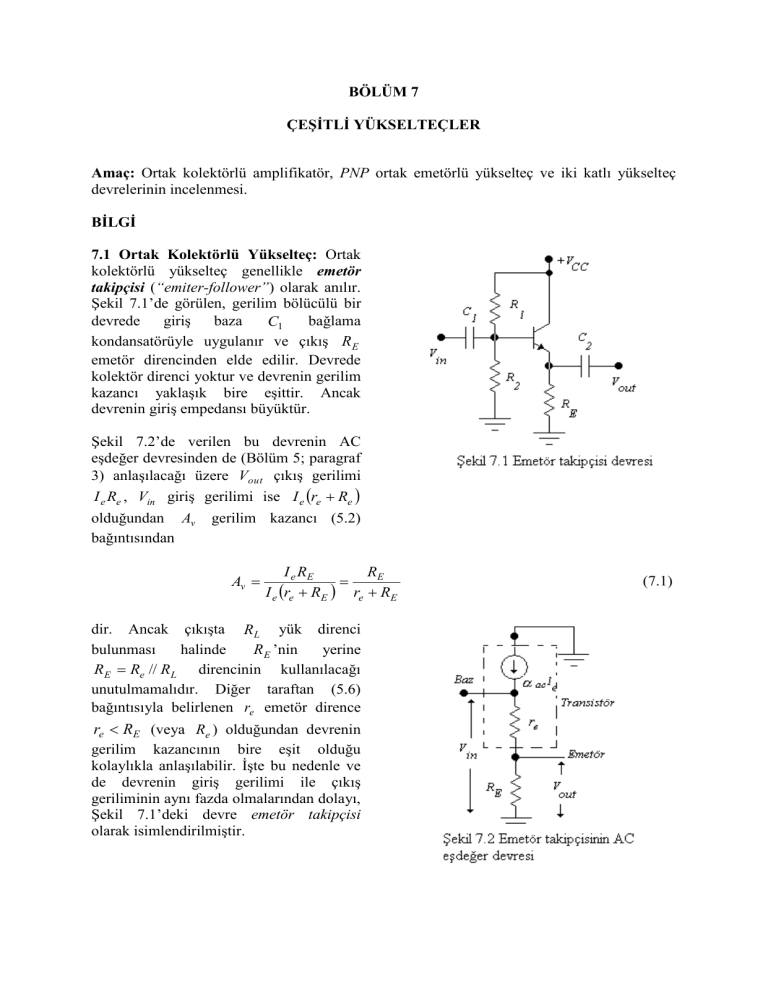

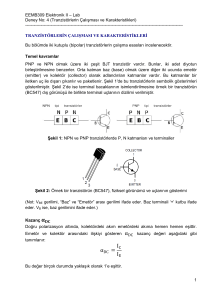

7.1 Ortak Kolektörlü Yükselteç: Ortak

kolektörlü yükselteç genellikle emetör

takipçisi (“emiter-follower”) olarak anılır.

Şekil 7.1’de görülen, gerilim bölücülü bir

devrede

giriş

baza

bağlama

C1

kondansatörüyle uygulanır ve çıkış R E

emetör direncinden elde edilir. Devrede

kolektör direnci yoktur ve devrenin gerilim

kazancı yaklaşık bire eşittir. Ancak

devrenin giriş empedansı büyüktür.

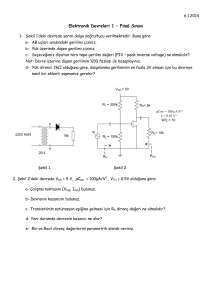

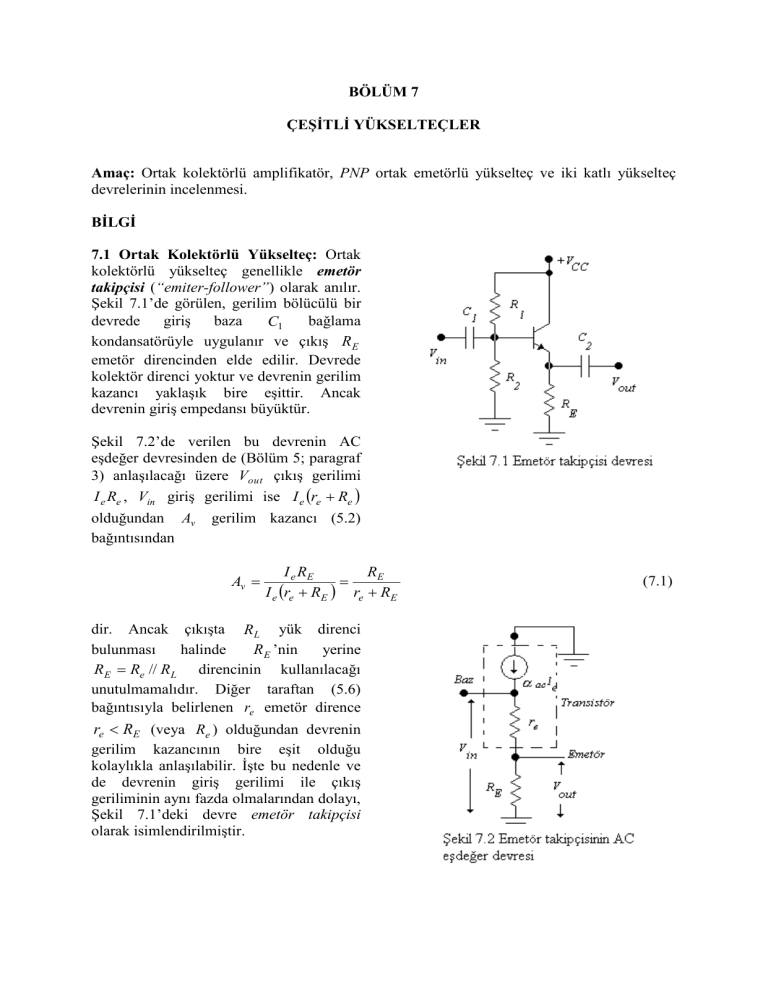

Şekil 7.2’de verilen bu devrenin AC

eşdeğer devresinden de (Bölüm 5; paragraf

3) anlaşılacağı üzere Vout çıkış gerilimi

I e Re , Vin giriş gerilimi ise I e re Re

olduğundan Av gerilim kazancı (5.2)

bağıntısından

Av

I e RE

RE

I e re RE re RE

dir. Ancak çıkışta R L yük direnci

bulunması

halinde

yerine

R E ’nin

RE Re // RL direncinin kullanılacağı

unutulmamalıdır. Diğer taraftan (5.6)

bağıntısıyla belirlenen re emetör dirence

re RE (veya Re ) olduğundan devrenin

gerilim kazancının bire eşit olduğu

kolaylıkla anlaşılabilir. İşte bu nedenle ve

de devrenin giriş gerilimi ile çıkış

geriliminin aynı fazda olmalarından dolayı,

Şekil 7.1’deki devre emetör takipçisi

olarak isimlendirilmiştir.

(7.1)

Emetör takipçisi devrenin en önemli özelliği yüksek giriş empedansına sahip olmasıdır: Bu

sayede iki devre arasında tampon (“buffer”) özelliğini sağlar. Bu devrenin bazdan görülen

Rint direnci, (5.7) bağıntısına göre

Rint

Vb I e re RE

Ib

Ib

dir. Ancak (5.5)’den

Rint

ac I b re RE

Ib

ac re RE

fakat RE re olduğundan

Rint ac RE

(7.2)

dir. Diğer taraftan girişten bakıldığında, R1 , R2 ve Rint dirençleri paralel bağlı olduklarından

transistörün Rin giriş empedansı

Rin R1 // R2 // Rint

(7.3)

bağıntısıyla belirlenebilir.

7.2 PNP Transistörlü Yükselteç:

Genellikle yükselteç devrelerinde npn

transistörler kullanılır.

Ancak pnp

transistör kullanarak, Şekil 5.1’deki

devrenin işlevi sağlanabilir: Burada en

önemli fark devrenin besleme geriliminin

negatif olmasıdır. Dolayısıyla Şekil 6.3’de

verilen devre negatif besleme gerilimi ile

Şekil 7.3’deki gibi düzenlenerek pnp

transistörlü devre elde edilebilir.

Şekil 7.3’deki devrede VB baz gerilimi,

baz akımı I B 0 ise

VB

R2

VCC

R1 R 2

(7.4)

VE emetör geriliminin, VBE 0,6V ise

VE VB 0,6

( 7.4 )

ve I C kolektör akımı, I E emetör akımına eşit, yani I C I E ise,

IC I E

VE

RE

( 7.4 )

dolayısıyla VC kolektör geriliminin

VC V CC I C RC

( 7.4 )

oldukları kolayca anlaşılabilir. Ayrıca bu devre için de (5.11) bağıntısı geçerli olduğundan;

fakat RE re için, Av gerilim kazancının

Av

RC

RE

(7.5)

olarak ifade dilebileceği açıktır.

7.3 Çok Katlı Amplifikatör: Bir çok yükseltici birbirinin çıkışına kademeli (“cascade”)

olarak, bir yükselticinin çıkışı diğerinin girişi olacak şekilde bağlanabilir. Bu şekilde her bir

yükselticinin kazancıyla böyle bir devrenin kazancı arttırılabilir. Bu takdirde her bir katın

gerilim kazancı sırasıyla Av1 , Av 2 , ise n katlı bir yükseltici devresinin Av toplam kazancı

Av Av1 Av 2

bağıntısıyla belirlenir.

(7.6)

DENEY

A)Ortak Kolektörlü Amplifikatör:

1)Digiac 3000 Semiconductors 2.1 modülünün 8 nolu düzeni yardımıyla Şekil 7.4’deki devre

gerçekleştirilir. 0-12V gerilim kaynağıyla devreye, DC voltmetre olarak kullanılan DM ile

ölçülerek 10V uygulanır.

2)DM ile sırasıyla VCQ kolektör, V BQ baz ve V EQ emetör sükunet gerilimleri ölçülür, sonuçlar

Tablo 7.1’e işlenir.

3)SG ile devreye uygulanacak sinüs işaretinin frekansı 1 kHz’ e ayarlanır ve çıkış genliği

minimum seviyeye getirilir.

Tablo 7.1

VCQ

V BQ

V EQ

4)Osiloskopla gözlenen ve baz ile emetör gerilimlerini belirleyen iki çizgi arasında yaklaşık

0,6V fark ( VBE 0,6V ) olduğuna dikkat edilir.

5)SG’nin çıkış genliği yavaş yavaş arttırılarak çıkış geriliminin bozulması (distorsiyon)

gözlenir. Sonra genlik azaltılarak çıkışta bozulma olmadan elde edilen maksimum gerilimin

p-p değeri olan V pp ölçülür, sonuç Tablo 7.2’ye geçirilir.

Tablo 7.2

V pp (V )

6)Osiloskopla gözlenen Vin giriş ve Vout çıkış gerilimleri çizilir.

7)SG’nin çıkış genliği tepeden tepeye 6V olacak şekilde ayarlanır. Osiloskopta gözlenen Vin

ve Vout gerilimlerinden gerilim kazancı belirlenir, sonuç Tablo 7.3’e geçirilir.

Tablo 7.3

Kazanç

8)Şekil 7.4’deki R15 direncindeki VR15 gerilim düşmesi AC voltmetre olarak kullanılan DM

ile ölçülür. Benzer şekilde yükselticinin Vin giriş gerilimi ve Vout çıkış gerilimi de ölçülür,

sonuçlar Tablo 7.4’e işlenir.

Rin giriş empedansı seri bağlı

Vin / Rin VR15 / R15 bağıntısından Rin hesaplanır, sonuç Tablo 7.4’e geçirilir.

9)R15

direnci

ile

transistörün

VR15 V

Tablo 7.4

Vout V

Vin V

Rin K

olduklarından,

Av

10) Vout ve Vin değerlerinden devrenin Av

kat gerilim kazancı (5.2) bağıntısından

hesaplanır, sonuç Tablo 7.4’e işlenir.

11)Yukarıda belirlenen Rin değerini

kontrol etmek amacıyla Şekil 7.4’deki

devrede, I b baz akımını ve I c kolektör

akımlarını ölçmek üzere Şekil 7.5’deki gibi

devreye DC ampermetre olarak kullanılan

DM bağlanır. Önce I b , sonra DM’nin yeri

değiştirilerek I c ölçülür, sonuçlar Tablo

7.5’ e geçirilir.

Tablo 7.5

Ib A

Ic mA

Rint K

Reş K

Rin K

12)Bu değerlerden, (4.2) bağıntısı yardımıyla transistörün h fe akım kazancı, (7.2)

bağıntısıyla da transistörün Rint giriş empedansı hesaplanır, sonuçlar Tablo 7.5’e işlenir.

13)Şekil 7.5’den de anlaşılacağı üzere R1 120K , R2 270K ve Rint dirençleri paralel

bağlı olduklarından devrenin Rin giriş empedansı (7.3) bağıntısından hesaplanır. Bunun için

Reş R1 // R2 ve Rin Reş // Rint dirençleri hesaplanır, sonuçlar Tablo 7.5’e geçirilir.

14)Bulunan bu sonuç yukarıda ölçüm sonucu belirlenen değerle karşılaştırılır.

B) PNP Ortak Emetörlü Yükselteç:

1)Digiac 3000 Semiconductors 2.1

modülünün 9 nolu düzeni yardımıyla Şekil

6.9’daki npn transistörlü devrenin benzeri

olan ve Şekil 7.6’da görülen devre

gerçekleştirilir(Bu devrede Şekil 6.9’daki

emetör kısa devre kondansatörü kullanılmamış, buna karşılık C7 kolektör kısa

devre kondansatöründen yararlanılmıştır).

2)Devreye –12V gerilimin uygulandığı

kabul edilerek devrenin sükunet şartları ,

V BQ baz gerilimi, V EQ emetör gerilimi,

VCQ kolektör gerilimi ve devrenin Av kat

gerilim kazancı (7.5) bağıntısıyla teorik

olarak hesaplanır, sonuçlar Tablo 7.6’ya

işlenir.

Tablo 7.6

VBQ V

VEQ V

VCQ V

Av

3)SG ile devreye uygulanacak sinüs işaretinin frekansı 1kHz’e ayarlanır ve çıkış genliği

minimum seviyeye getirilir.

4)DC voltmetre olarak kullanılan DM ile, sırasıyla Vc kolektör, Vb baz ve Ve emetör

gerilimleri ölçülerek, sonuçlar Tablo 7.7’ye geçirilir.

Tablo 7.7

Vc V

Vb V

Ve V

5)Ölçülen bu değerler, Tablo 7.6’da hesaplananlarla karşılaştırılır.

6)SG’nin çıkış genliği arttırılarak Vin giriş geriliminin p-p 1V olması sağlanır.

7)Osiloskopla Vout p-p çıkış gerilimi ölçülerek, sonuç Tablo 7.8’e işlenir.

8)Bu değerlerden (5.2) bağıntısı yardımıyla devrenin Av gerilim kazancı hesaplanır, sonuç

Tablo 7.8’e geçirilir.

Tablo 7.8

Vin V

p p

Vout V

Av

p p

C) İki Katlı Yükseltici:

1)Digiac 3000 Semiconductors 2.1 modülünün 8 ve 9 nolu düzenlerinden yararlanılarak Şekil

7.4 ve Şekil 7.6’da görülen devrelerin, ufak değişikliklerle beraberce oluşturulması gibi

görünen Şekil 7.7’deki devre gerçekleştirilir.

2)SG ile devreye uygulanacak sinüs işaretinin frekansı 1kHz’e ayarlanır ve çıkış genliği

minimum seviyede tutulur.

3)0-12V gerilim kaynağı ile npn transistörlü devreye 10V uygulanır.

4)SG’nin genliği arttırılarak birinci kat yükseltici girişinde p-p 10mV gerilim elde edilir. Bu

durumda çıkış gerilimi okunarak, Tablo 7.9’a işlenir.

5)Bu değerlerden birinci katın Av1 gerilim kazancı hesaplanır, sonuç Tablo 7.9’a geçirilir.

Tablo 7.9

Vin1

p p

Vout1

p p

Av1

Vout2

p p

Av

Av Av1 Av 2

Hesap

6)DC gerilim ölçmek üzere kullanılan DM ile pnp transistörün

ölçülür, sonuç Tablo 7.10’a işlenir.

VC , pnp kolektör gerilimi

7)Şekil 7.4’deki devrede A ve B noktaları birleştirilir. Böylece birinci npn ve ikinci kat pnp

yükselteçleri birleştirilmiş olur. Bu durumda pnp transistörün VCAB kolektör gerilimi tekrar

ölçülür. Sonuç Tablo 7.10’a geçirilir ve nedeni açıklanır.

Tablo 7.10

VC , pnp (V )

VCAB

VCAC (V )

8)Bu sefer A ve C noktaları birleştirilerek C6 izolasyon kondansatörlü iki kat yükselteç

devresi oluşturulur, VCAC kolektör gerilimi tekrar belirlenir. Sonuç Tablo 7.10’a yazılır ve

yorumlanır.

9)A ve C noktaları birleştirilmeden ve birleştirilerek osiloskopla birinci kat yükselticinin

çıkışındaki gerilimin nasıl değiştiği gözlenir ve nedeni araştırılır.

10)Osiloskop yardımıyla iki katlı yükseltecin ikinci katının Vo u 2t çıkış gerilimi ölçülür ve

Tablo 7.9’daki değerlerden faydalanılarak iki katlı yükseltecin Av gerilim kazancı hesaplanır,

sonuçlar Tablo 7.9’a işlenir.

11)Tablo 7.6 ve 7.9’daki değerlerden iki katlı yükselticinin toplam gerilim kazancı hesaplanır,

sonuç Tablo 7.9’a geçirilir.

10)Bu devrenin giriş ve çıkışında osiloskopla gözlenen gerilimler çizilir.

SORULAR

1)Ortak kolektörlü (emetör takipçisi) yükseltecin gerilim kazancı ile güç kazançları ne

kadardır? Bu yükseltecin giriş ve çıkış empedanslarının özellikleri nelerdir?

2)Ortak kolektörlü yükseltecin giriş empedansının belrilenmesi amacıyla üzerindeki gerilim

düşmesi 235mV olan 47K’lık bir direnç girişe seri olarak bağlanmıştır. Yükseltecin giriş

gerilimi 1,5V ise giriş empedansı ne kadardır?

3)Şekil 7.6’daki devrede baz-emetör gerilimi 0,6V ise toprağa göre kolektör gerilimi nedir?

4)Bir yükseltecin çıkış empedansı (kolektör yük direnci) 3,9K ve bir diğerinin giriş direnci

8,5K’dır. İlk yükseltecin yüksüz çıkış gerilimi p-p 4V ise ikincisi bağlandığında bu katın giriş

gerilimi nedir?