BÖLÜM 8

FARK YÜKSELTEÇ

Amaç: Fark yükseltecin çalışmasının incelenmesi ve kazancının belirlenmesi

BİLGİ

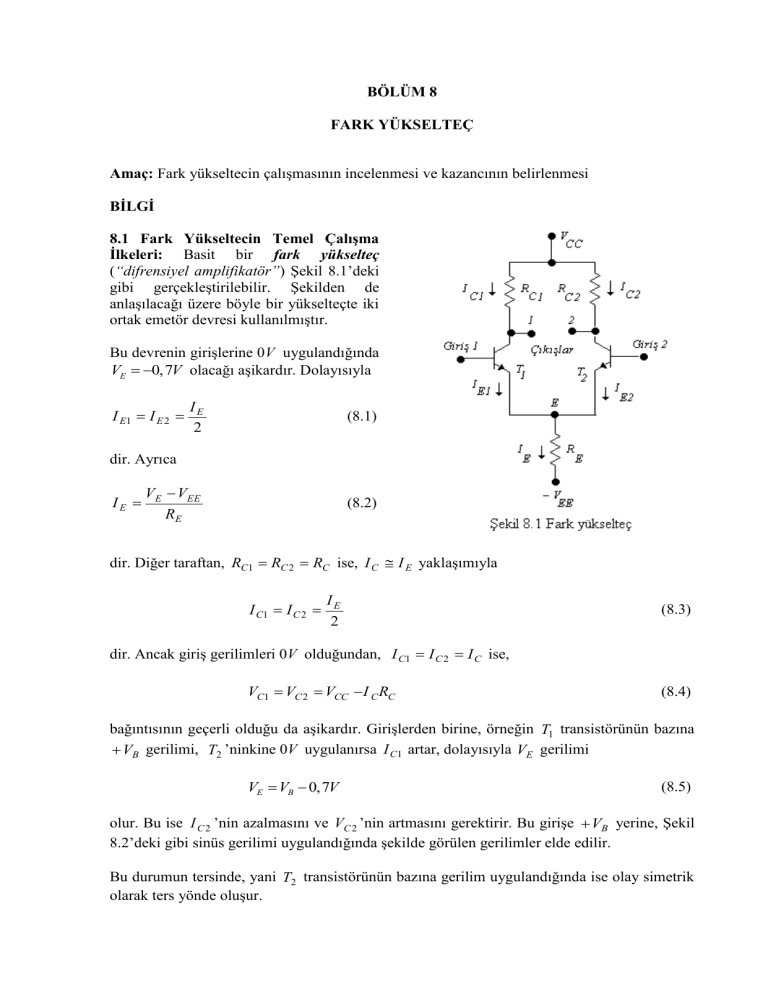

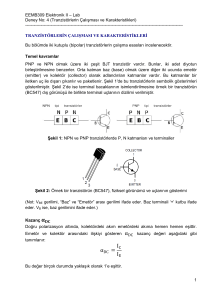

8.1 Fark Yükseltecin Temel Çalışma

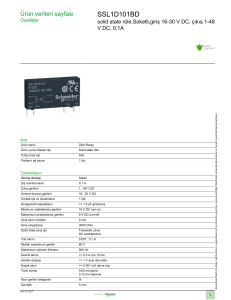

İlkeleri: Basit bir fark yükselteç

(“difrensiyel amplifikatör”) Şekil 8.1’deki

gibi gerçekleştirilebilir. Şekilden de

anlaşılacağı üzere böyle bir yükselteçte iki

ortak emetör devresi kullanılmıştır.

Bu devrenin girişlerine 0V uygulandığında

VE 0,7V olacağı aşikardır. Dolayısıyla

IE

2

(8.1)

VE VEE

RE

(8.2)

I E1 I E 2

dir. Ayrıca

IE

dir. Diğer taraftan, RC1 RC 2 RC ise, I C I E yaklaşımıyla

I C1 I C 2

IE

2

(8.3)

dir. Ancak giriş gerilimleri 0V olduğundan, I C1 I C 2 I C ise,

VC1 VC 2 VCC I C RC

(8.4)

bağıntısının geçerli olduğu da aşikardır. Girişlerden birine, örneğin T1 transistörünün bazına

VB gerilimi, T2 ’ninkine 0V uygulanırsa I C1 artar, dolayısıyla VE gerilimi

VE VB 0,7V

(8.5)

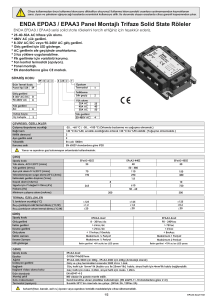

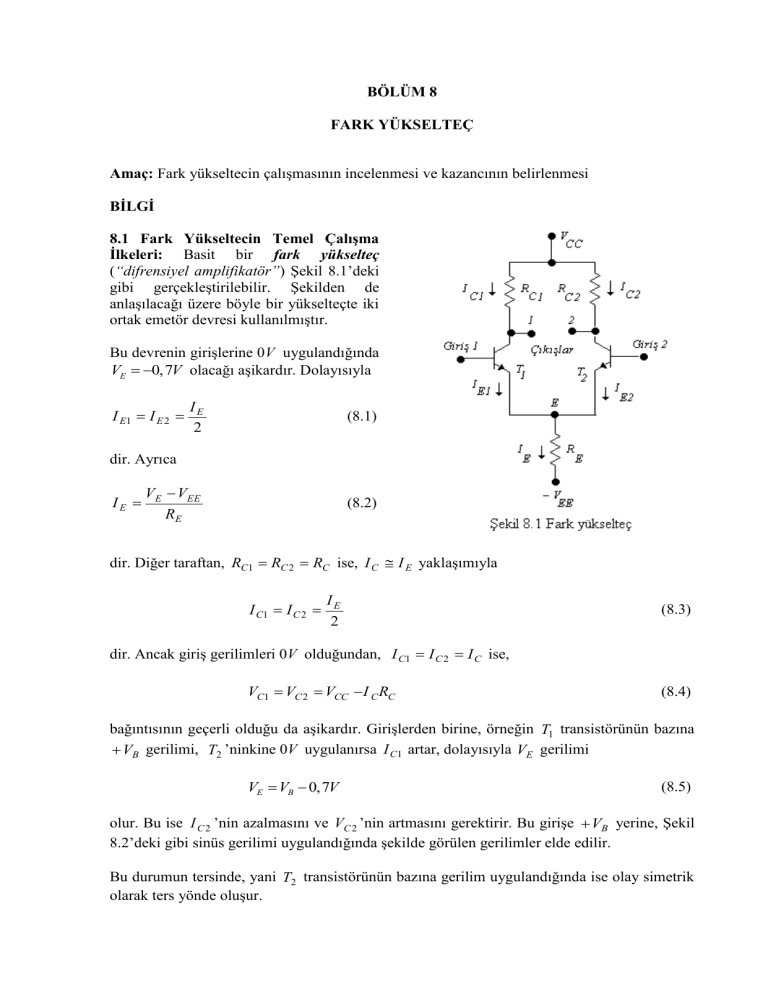

olur. Bu ise I C 2 ’nin azalmasını ve VC 2 ’nin artmasını gerektirir. Bu girişe VB yerine, Şekil

8.2’deki gibi sinüs gerilimi uygulandığında şekilde görülen gerilimler elde edilir.

Bu durumun tersinde, yani T2 transistörünün bazına gerilim uygulandığında ise olay simetrik

olarak ters yönde oluşur.

8.2 Fark Çıkışı: Şekil 8.2’den de görüleceği gibi, birbirlerinin eşi iki transistörlü devreden

oluşmuş bir fark yükseltecinin girişlerine eşit frekans, genlik ve fazda iki gerilim

uygulandığında, devrenin 1 ve 2 çıkışları arasındaki gerilim farkı teorik olarak sıfırdır. Ancak

girişe uygulanan gerilimlerin, örneğin genlikleri arasında bir fark varsa bu fark arttırılarak

çıkışa yansır ve çıkışlar arasındaki gerilim farkından söz edilir.

DENEY

A) DC Sükunet Şartlarının Belirlenmesi:

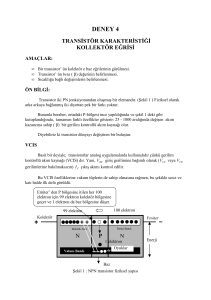

1)Digiac 3000-2.2 Semiconductors-2 modülünün 4 nolu düzeni yardımıyla Şekil 8.3’deki

devre gerçekleştirilir.

2)1K’lık potansiyometre (VR-3) ile direnç azaltıldığında (ayar düğmesi saat ibresi yönünde

çevrildiğinde) , dolayısıyla TR6 transistörünün baz akımı arttırıldığında, bu transistörün, DC

voltmetre olarak kullanılan DM ile ölçülen giriş geriliminin yükseldiği ve osiloskopla izlenen

kolektör geriliminin azaldığı; buna karşılık TR7 ’nin kolektör geriliminin arttığı gözlenir.

3)VR-3 potansiyometresi ile direnç değiştirilerek, TR7 ’in kolektör gerilimi olan VC 7 , DM ile

7V’a ayarlanır.

4)Bu durumda DM ile iki kolektör gerilimi arasındaki gerilim farkı, yani Vout çıkış fark

gerilimi ölçülür, sonuç Tablo 8.1’e geçirilir.

Tablo 8.1

VC 7 V

Vout V

7

5)VR-3 potansiyometresiyle bu gerilim farkı azaltılarak yaklaşık sıfır olması sağlanır.

6)Bu durumda TR6 ve TR7’nin kolektör, baz ve emetör gerilimleri ile ikisinin ortak emetör

bağlantısının (A noktası) gerilimi DM ile ölçülerek sonuçlar Tablo 8.2’ye işlenir.

Tablo 8.2

TR6

Kolektör(V)

Baz(mV)

TR7

Emetör(V)

Kolektör(V) Baz(mV) Emetör(V)

Ortak

emetör(V)

7)Devre elemanlarının değerlerinden ve bu tablodaki ortak emetör geriliminden yararlanılarak

(8.2) bağıntısıyla I E akımı, (8.1) bağıntısı ve Ohm kanunu kullanılarak da transistörlerin

emetör akım ve gerilimleri hesaplanır. Ayrıca (8.3) ve (8.4) bağıntılarından yararlanılarak

transistörlerin kolektör akımı ile gerilimleri hesaplanır, sonuçlar Tablo 8.3’e geçirilir.

Hesaplanan bu sonuçlar Tablo 8.2’deki değerlerle karşılaştırılır.

Tablo 8.3

I E mA

I E 6 mA

VE 6 V

IC 6 mA

VC 6 V

B) AC Gerilim Kazancının Ölçülmesi:

1)Şekil 8.3’deki devrede bazı değişiklikler yapılarak Şekil 8.4’deki devre gerçekleştirilir. SG

ile devreye uygulanacak sinüs işaretinin frekansı 1kHz’e ayarlanır ve çıkış genliği minimum

seviyeye getirilir.

2)Sinüs işaretinin genliği arttırılarak TR6 transistörünün osiloskopla ölçülen kolektör

geriliminin p-p 8V olması sağlanır.

3)TR6 transistörünün osiloskopla gözlenen Vb 6 ve Vc 6 giriş ve çıkış gerilimleri çizilir.

4)Osiloskopla TR6’nın Ve 6 emetör gerilimi gözlenir ve aynı eğri üzerine çizilir.

5)TR7 transistörünün de Vc 7 kolektör gerilimi osiloskopla gözlenir ve görüntü aynı eğriye

çizilir.

6)AC voltmetre olarak kullanılan DM ile TR6 transistörünün Vb 6 ve Vc 6 , yani giriş ve çıkış

gerilimleri ölçülür. Benzer şekilde TR7 transistörünün Vc 7 çıkış gerilimi de okunur. Sonuçlar

Tablo 8.4’e işlenir.

Tablo 8.4

Giriş İşareti(V)

TR6 çıkışı(V)

TR7 çıkışı(V)

Fark gerilimi(V)

7)Devrenin çıkış fark gerilimi DM ile ölçülür, sonuç Tablo 8.4’e geçirilir.

8)Tablo 8.4’deki değerlerden, (5.2) bağıntısı kullanılarak TR6 ve TR7’nin kat kazançları ile

devrenin fark kazancı hesaplanır, sonuçlar Tablo 8.5’e geçirilir.

Tablo 8.5

TR1 Kat kazancı

TR2 Kat kazancı

Fark kazancı

SORULAR

1)Bir fark yükselteçte bir transistörün kolektör akımı artarsa bu ve diğer transistörün kolektör

gerilimleri nasıl değişir?

2)Fark yükselteçte bir transistörün girişine pozitif bir işaret, diğerine 0V uygulanırsa iki

transistörün kolektör gerilimleri ne olur?

3) Fark yükseltecin transistörlerinin kolektör gerilimlerinin arasındaki fark gerilimi 0V ise

transistörlerin girişlerine hangi işaretler uygulanmıştır?

4)Şekil 8.3’deki devrede TR6 transistörünün kolektör gerilimi +5,5V ise TR7 transistörünün

kolektör ve emetör gerilimleri nedir?