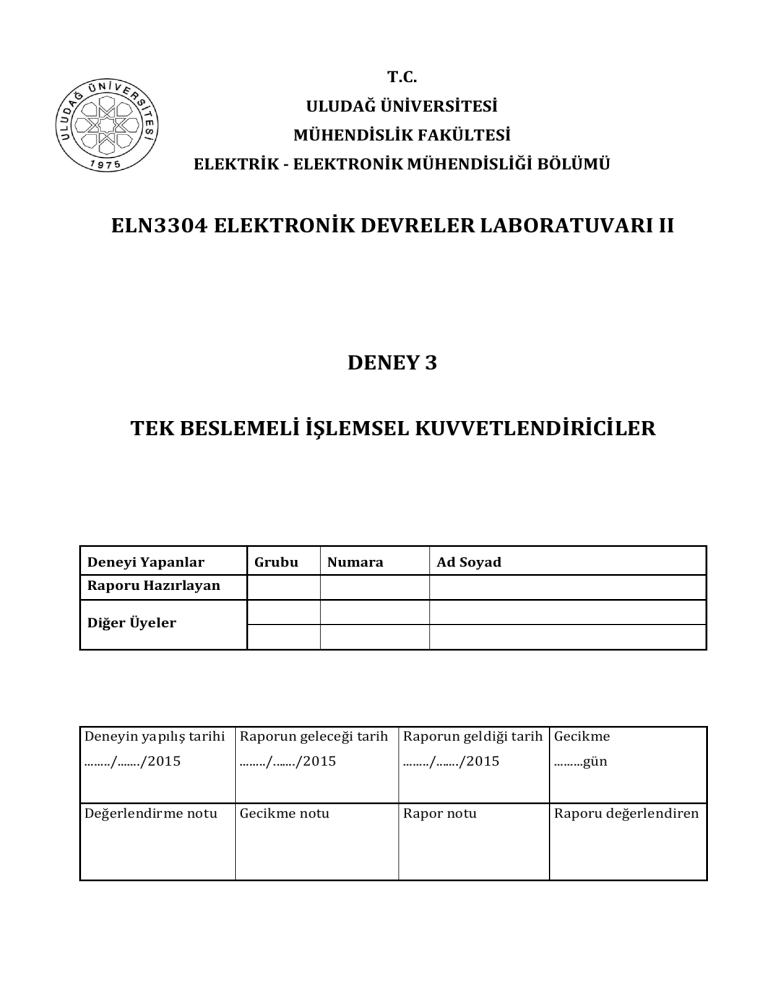

T.C.

ULUDAĞ ÜNİVERSİTESİ

MÜHENDİSLİK FAKÜLTESİ

ELEKTRİK - ELEKTRONİK MÜHENDİSLİĞİ BÖLÜMÜ

ELN3304 ELEKTRONİK DEVRELER LABORATUVARI II

DENEY 3

TEK BESLEMELİ İŞLEMSEL KUVVETLENDİRİCİLER

Deneyi Yapanlar

Grubu

Numara

Ad Soyad

Raporu Hazırlayan

Diğer Üyeler

Deneyin yapılış tarihi Raporun geleceği tarih Raporun geldiği tarih Gecikme

......../......./2015

......../......./2015

......../......./2015

.........gün

Değerlendirme notu

Gecikme notu

Rapor notu

Raporu değerlendiren

ELN3304 ELEKTRONİK DEVRELER LABORATUVARI II

DENEY NO:3

DENEY 3: TEK BESLEMELİ İŞLEMSEL KUVVETLENDİRİCİLER

I. ÖN BİLGİ

Op-Amp (Operational Amplifier, İşlemsel kuvvetlendirici) geribeslemesiz durumda çok büyük

kazanca sahip tümleşik bir devredir. Op-Ampların iki girişi tek çıkışı vardır. Girişlerden biri faz çeviren

diğeri ise faz çevirmeyen giriştir. Çıkış ile faz çeviren giriş arasına bir direnç bağlanırsa negatif

geribesleme gerçekleştirilmiş olur. Benzer şekilde çıkış ile faz çevirmeyen giriş arasına bir direnç

bağlanırsa pozitif geribesleme elde edilmiş olur.

Op-Amplar hem kuvvetlendirme yapan hem de giriş işaretleri üzerinde işlem yapan elemanlardır.

Op-Amplar ile çeşitli işlemler yapılabilir: gerilim izleyici, ideal diyot devresi, faz çeviren ve çevirmeyen

kuvvetlendirici, toplama ve fark devreleri, integral, türev ve logaritma alıcı devreler.

Günümüzde bir kılıf içerisinde bir adet, iki adet veya dört adet Op-Amp içeren entegreler vardır.

Genelde bir kılıf içerisinde birden fazla Op-Amp olduğundan Op-Ampların besleme uçları ortaktır.

Kılıfta kullanılmayan Op-Ampların giriş uçları toprağa veya beslemeye bağlanmalıdır. Genellikle

kullanılmayan Op-Ampların giriş uçları toprağa bağlanır.

Op-Amplar genelde çift beslemelidirler, fakat gerekli bağlantılar yapılarak tek beslemeli olarak da

çalıştırılabilirler. Ancak burada AC işaret kuvvetlendirme durumunda, kuvvetlendirilen işaretin genliği

besleme geriliminin yarısı ile sınırlıdır. Girişte AC işaret olmadığı durumda çıkışta bir DC işaretin

olması tek beslemeli devrenin bir dezavantajıdır. Çıkışta DC işareti süzmek için bir kondansatör

kullanmak gerekir. Kuvvetlendirilecek işaret AC ise çift besleme, tek polariteli ise (örneğin darbe

kuvvetlendiricilerde) tek besleme kullanmak daha mantıklıdır.

II. DENEYİN AMACI

Op-Amplar ile çeşitli işlem yapan devreleri incelemek. Op-amplı devrelerin önemli

karakteristiklerini deneysel elde etmek. Tek beslemeli Op-Amplar ile çift beslemeli Op-Ampların

avantaj ve dezavantajlarını belirlemek.

III. DENEYDE KULLANILACAKLAR

Deney bordu, çift kanallı osiloskop, dijital ölçü aleti

LM324 op-amp tümdevresi,

Kondansatör: 220nF/63V

Dirençler: 1k(2 adet), 5,6k(1 adet), 10k(3 adet), 56k(2 adet), 100k(2 adet)

2/7

ELN3304 ELEKTRONİK DEVRELER LABORATUVARI II

DENEY NO:3

IV. ÖN HAZIRLIK

1. Op-Ampın iç yapısında hangi devre elemanları kullanılır?

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

2. Gerilim izleyici nedir? Kazancı kaçtır? Hangi amaçla kullanılır?

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

3. Şekil 6.4’de gösterilen tek beslemeli faz çeviren kuvvetlendirici devresinin kazanç ifadesini bulunuz.

Faz çeviren kuvvetlendiricinin girişine sinüzoidal bir işaret uygulanır ise giriş ve çıkış işaretleri nasıl

oluşur alt alta çizerek gösteriniz.

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

4. Şekil 6.5’de gösterilen tek beslemeli faz çevirmeyen kuvvetlendirici devresinin kazanç ifadesi

bulunuz. Faz çevirmeyen kuvvetlendiricinin girişine sinüzoidal bir işaret uygulanır ise giriş ve çıkış

işaretleri nasıl oluşur alt alta çizerek gösteriniz.

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

3/7

ELN3304 ELEKTRONİK DEVRELER LABORATUVARI II

DENEY NO:3

5. Tek beslemeli Op-Ampların avantaj ve dezavantajları nelerdir?

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

6. Çift beslemeli Op-Ampların avantaj ve dezavantajları nelerdir?

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

V. DENEYİN YAPILIŞI

1. Şekil 6.1’de gösterilen LM324 entegresi ile geliştirilmiş gerilim izleyici devresini kurunuz. Aşağıdaki

tabloda verilen giriş gerilimleri için çıkış gerilimini ölçünüz ve aşağıdaki tabloya yazınız.

13

14

12

-

4

LM324

3

+

10

9

8

GND

+5V

2

11

-

+

+

4

1

3

Uç

11

+15V

-

R1

LM324

Ug

+

+

-

-

1

UG

V+

1

(V)

Çıkış gerilimi

ç (V)

3

4

5

6

-1

0

1

-

4

1

A

R2

3

+

B

Uç

11

56k

7

Şekil 6.2. LM324

Şekil 6.1. Gerilim izleyici.

Giriş gerilimi

2

220nF

2

LM324

C

2

56k

Şekil 6.3. AC girişli gerilim izleyici.

2

3

4

5

6

7

Kazanç ( ç ⁄ )

2. Şekil 6.3’de gösterilen gerilim izleyici devresini kurunuz. Devrenin girişine herhangi bir işaret

uygulamadan A ve B noktalarındaki gerilimleri ölçü aleti ile ölçünüz ve aşağıdaki tabloya yazınız.

(V)

(V)

4/7

ELN3304 ELEKTRONİK DEVRELER LABORATUVARI II

DENEY NO:3

3. Şekil 6.3’de gösterilen gerilim izleyici devrenin girişine 1kHz’lik sinüzoidal bir işaret uygulayınız.

Farklı giriş işaretleri genlikleri

için çıkış işaretleri genliklerini ( ç = ç ⁄2) ölçünüz. Ölçtüğünüz

giriş ve çıkış işaretlerinin değerlerini aşağıdaki tabloya yazınız. Kazancı hesaplayınız.

Giriş gerilimi

2

(V)

Çıkış gerilimi

ç

Kazanç

ç

=

3

4

5

6

7

8

9

(V)

4. Şekil 6.4’de gösterilen devrenin girişine sinüzoidal bir işaret uygulayınız. Giriş işaretinin genliğini

sabit tutunuz. Giriş işaretinin frekansını sıfırdan 1 MHz’e kadar değiştirerek kazancın frekans ile

değişimini araştırınız. Giriş ve çıkış işaretlerinin değerlerini aşağıdaki tabloya yazınız ve kazancı

hesaplayınız.

Frekans f, kHz

Çıkış gerilimi

ç

Kazanç

ç

=

(V)

5. Şekil 6.4’de gösterilen devreyi kurunuz. Girişe herhangi bir işaret uygulamadan A, B ve C

noktalarındaki gerilimleri ölçü aleti ile ölçünüz ve aşağıdaki tabloya yazınız. Devrenin girişine 1kHz’lik

sinüzoidal gerilim uygulayınız. Giriş işaretinin genliğini çıkışta kırpılma olmayacak şekilde ayarlayınız.

A, B ve C noktalarındaki işaretleri çift kanallı osiloskopla ölçünüz ve aşağıdaki grafikler üzerine çiziniz.

(V)

Rf=10k

UG

C A R1

220nF 1k

R2

100k

+15V

B

2

10k

3

-

(V)

UG

+15V

4

LM324

+

(V)

11

10k

1

Ry

5,6k

0

C

UÇ

t

UA

0

Şekil 6.4. Tek

kuvvetlendirici

beslemeli

faz

çeviren

UB

0

t

UC

0

6. Şekil 6.5’de gösterilen devreyi kurunuz. Devrenin girişine herhangi bir işaret uygulamadan A, B ve C

noktalarındaki gerilimleri ölçü aleti ile ölçünüz aşağıdaki tabloya yazınız. Devrenin girişine 1kHz’lik

sinüzoidal gerilim uygulayınız. Giriş işaretinin genliğini çıkışta kırpılma olmayacak şekilde ayarlayınız.

A, B ve C noktalarındaki işaretleri çift kanallı osiloskopla ölçünüz ve aşağıdaki grafikler üzerine çiziniz.

5/7

t

ELN3304 ELEKTRONİK DEVRELER LABORATUVARI II

R4

100nF

C2

10k

C1

UG

(V)

(V)

UG

+15V

2

A

-

LM324

3

+

Uç

11

UA

Ry

5,6k

R1 100k

R3

10k

C

1

t

0

4

220nF

+15V R2

(V)

Rf=100k

B

DENEY NO:3

t

0

10k

UB

Şekil 6.5. Tek beslemeli faz çevirmeyen

kuvvetlendirici devresi.

t

0

UC

t

0

7. Şekil 6.6’da gösterilen devreyi kurunuz. Devrenin girişine 1kHz’lik bir kare dalga uygulayınız. Giriş

işaretinin genliğini kuvvetlendirici doyuma girmeyecek şekilde ayarlayınız. Giriş ve çıkış işaretlerini

aşağıdaki grafik üzerinde çizerek gösteriniz.

UG

Rf=100k

+15V

R1

2

1k

UG

-

4

LM324

3

+

0

1

Uç

Ry

5,6k

11

t

UÇ

0

t

Şekil 6.6. Tek beslemeli faz çeviren

kare darbe kuvvetlendirici devresi

8. Şekil 6.7’de gösterilen devreyi kurunuz. Girişine 1kHz’lik bir kare dalga uygulayınız. Giriş işaretinin

genliğini kuvvetlendirici doyuma girmeyecek şekilde ayarlayınız. Giriş ve çıkış işaretlerini aşağıdaki

grafik üzerinde çizerek gösteriniz.

UG

Rf =10k

R1 1k

+15V

2

-

LM324

3

UG

10k R2

+

0

4

t

1

Uç

11

Ry

UÇ

5,6k

0

Şekil 6.7. Tek beslemeli faz çevirmeyen kare darbe kuvvetlendirici

devresi

6/7

t

ELN3304 ELEKTRONİK DEVRELER LABORATUVARI II

DENEY NO:3

VI. RAPORDA İSTENENLER

1. 3. adımda elde ettiğiniz değerlerden yararlanarak ç = ( ) grafiğini çiziniz ve doyum bölgesini

tespit ediniz.

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

2. 4. adımda elde değerlerden yararlanarak Şekil 6.4’deki devrenin frekans karakteristiğini çiziniz.

3. Şekil 6.4’deki devrede R2 direnci çıkış gerilimini nasıl etkiler?

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

4. Şekil 6.5’deki devrede C2 kondansatörünün görevini açıklayınız.

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

…………………………………………………………………………………………………………………………………………………………

7/7