LABORATUVAR ÇALIŞMASI – 10

Basit İşlemci – II

Laboratuvar Çalışması – 9’da basit bir işlemci tanımlamıştık. Uygulama I ’de işlemcinin kendisini

tanımladık, Uygulama II ’de de bu işlemciyi bir sayıcı ve hafıza birimine bağladık. Bu çalışmada ise işlemci

tasarlamanın daha sonraki adımlarını gerçekleyeceğiz. Bu çalışmadaki şekil ve tablolar bir önceki çalışmanın

devamıdır.

Uygulama III

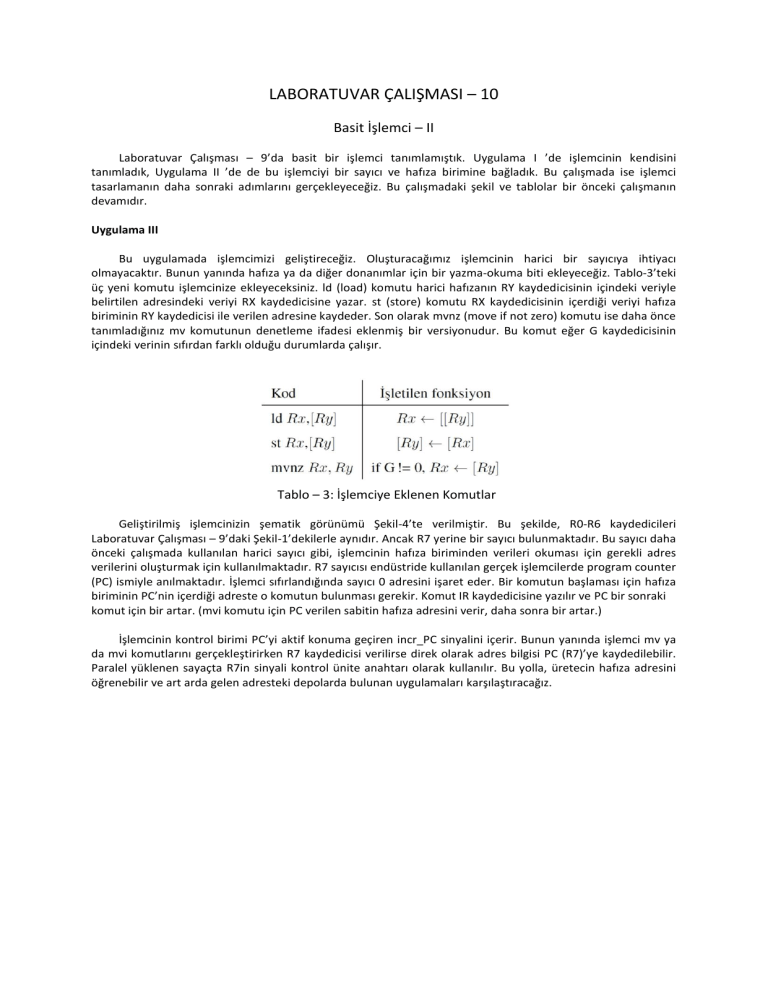

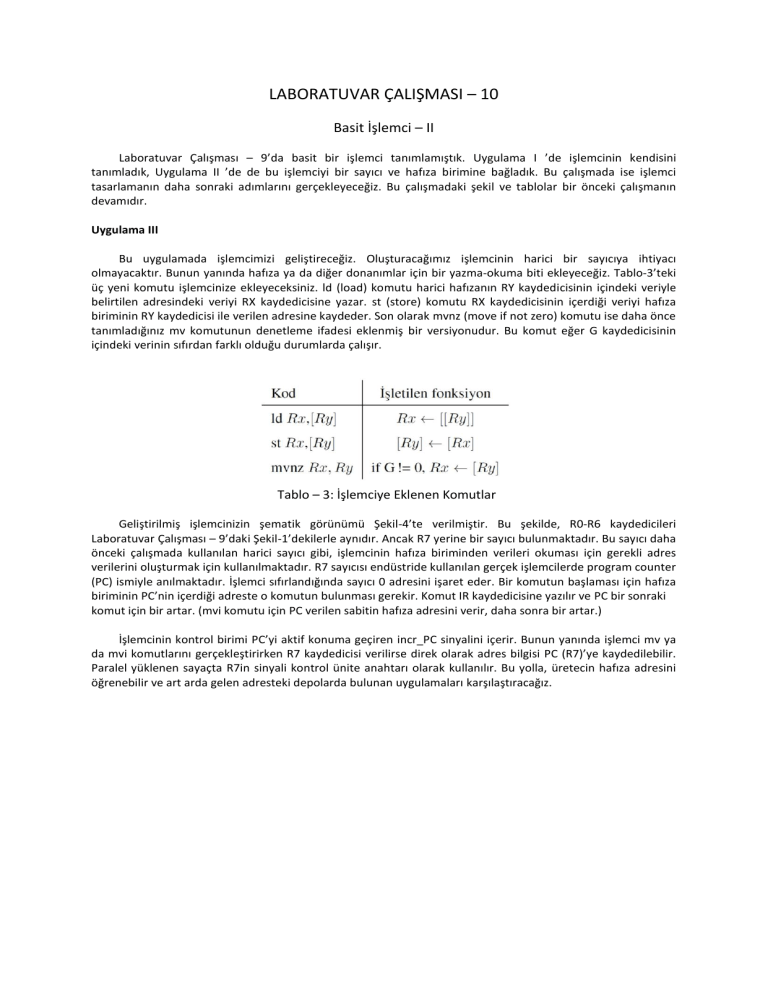

Bu uygulamada işlemcimizi geliştireceğiz. Oluşturacağımız işlemcinin harici bir sayıcıya ihtiyacı

olmayacaktır. Bunun yanında hafıza ya da diğer donanımlar için bir yazma-okuma biti ekleyeceğiz. Tablo-3’teki

üç yeni komutu işlemcinize ekleyeceksiniz. ld (load) komutu harici hafızanın RY kaydedicisinin içindeki veriyle

belirtilen adresindeki veriyi RX kaydedicisine yazar. st (store) komutu RX kaydedicisinin içerdiği veriyi hafıza

biriminin RY kaydedicisi ile verilen adresine kaydeder. Son olarak mvnz (move if not zero) komutu ise daha önce

tanımladığınız mv komutunun denetleme ifadesi eklenmiş bir versiyonudur. Bu komut eğer G kaydedicisinin

içindeki verinin sıfırdan farklı olduğu durumlarda çalışır.

Tablo – 3: İşlemciye Eklenen Komutlar

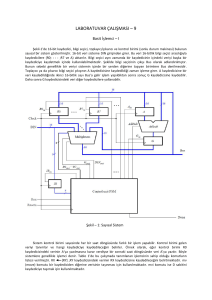

Geliştirilmiş işlemcinizin şematik görünümü Şekil-4’te verilmiştir. Bu şekilde, R0-R6 kaydedicileri

Laboratuvar Çalışması – 9’daki Şekil-1’dekilerle aynıdır. Ancak R7 yerine bir sayıcı bulunmaktadır. Bu sayıcı daha

önceki çalışmada kullanılan harici sayıcı gibi, işlemcinin hafıza biriminden verileri okuması için gerekli adres

verilerini oluşturmak için kullanılmaktadır. R7 sayıcısı endüstride kullanılan gerçek işlemcilerde program counter

(PC) ismiyle anılmaktadır. İşlemci sıfırlandığında sayıcı 0 adresini işaret eder. Bir komutun başlaması için hafıza

biriminin PC’nin içerdiği adreste o komutun bulunması gerekir. Komut IR kaydedicisine yazılır ve PC bir sonraki

komut için bir artar. (mvi komutu için PC verilen sabitin hafıza adresini verir, daha sonra bir artar.)

İşlemcinin kontrol birimi PC’yi aktif konuma geçiren incr_PC sinyalini içerir. Bunun yanında işlemci mv ya

da mvi komutlarını gerçekleştirirken R7 kaydedicisi verilirse direk olarak adres bilgisi PC (R7)’ye kaydedilebilir.

Paralel yüklenen sayaçta R7in sinyali kontrol ünite anahtarı olarak kullanılır. Bu yolla, üretecin hafıza adresini

öğrenebilir ve art arda gelen adresteki depolarda bulunan uygulamaları karşılaştıracağız.

Şekil – 4: İşlemcinin Geliştirilmiş Versiyonu

Şekil-4’teki işlemcide veri transferi için kullanılan iki kaydedici vardır. ADDR kaydedicisi Hafıza bloğu gibi

harici bir modüle adres bilgisini göndermek için kullanılırken, DOUT verinin harici modüllere gönderilmesini

sağlar. ADDR kaydedicisi okuma ve yazma olarak iki farklı şekilde kullanılır. Bunlardan biri hafızadan komutların

okunması (fetching) için PC (R7)’deki adres bilgisinin bu kaydediciye yüklenmesidir. Bu adres hafıza birimine

gönderilir ve ilgili veri DIN girişinden işlemciye ulaşır. Diğer kullanım ise işlemcinin elde ettiği sonuçların DOUT

kaydedicisi yardımıyla hafıza biriminin ADDR kaydedicisindeki adresine çıkış değerinin yazılmasıdır. Bu

kullanımlar W (write) yaz-bozu yardımıyla yönetilir (0 hafızadan okuma, 1 hafızaya yazma).

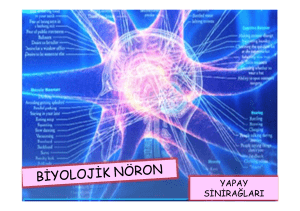

Şekil-5’te işlemcinin hafıza birimleri ya da diğer aygıtlarla nasıl bağlandığı gösterilmiştir. Şekildeki hafıza

birimi yazma ve okuma işlemlerini içermektedir. Birimin adres ve veri girişlerinin haricinde yazma okuma

işlevlerinin yönetilmesini sağlayan write_enable kontrol ucu ve veri iletişimini düzenlemek için saat ucu

bulunmaktadır.

Aktif saat tetiklemesinde adres, veri ve write_enable kontrol verisi hafıza birimine yüklenir. Bu tarz hafıza

birimlerine senkron rastgele erişimli hafıza birimi (synchronous random access memory (synchronous RAM)

denir. ¸ Sekil-5’da ayrıca işlemcideki bilgilerin yüklenebilmesi için kullanılabilecek 16-bitlik bir kaydedicide

gösterilmiştir. Bu kaydedici ledlere bağlanarak verilerin gösterilmesi sağlanabilir. İşlemcinin yazma işlemini

hafızaya mı yoksa bu kaydediciye mi yapacağının anlaşılması eklenen bir mantık devresinin adres bilgisinin

çözümlemesiyle (address decoding) yapılmaktadır. Eğer adres verisinin en anlamlı dört biti A15A14A13A12 =

0000 ise en anlamsız n bit hafıza birimine adres bilgisi olarak gönderilir. Buradaki örnekte hafıza birimi 128

kelime kapasiteye sahiptir. Bu yüzden n = 7 olarak alınır ve hafıza birimine A6 : : :A0 bitler adres bilgisi olarak

gönderilir. Eğer en anlamlı dört bit A15A14A13A12 = 0001 ise bu sefer işlemciden gelen veri ledlere bağlı olan

kaydediciye yazılır.

Şekil – 5: İşlemcinin Hafıza Birimi ve Kaydediciye Bağlanması

1) İşlemcinin gelişmiş versiyonu için yeni bir ISE Design Suite projesi oluşturun.

2) İşlemci için Verilog kodunu oluşturup DIN girişine komutları vererek fonksiyonel simülasyon yapın.

İşlemci ile Hafıza birimi arasındaki zamanlamaya dikkat edin.

3) Başka bir proje oluşturarak Şekil-5’teki yapıyı oluşturun. Bunun için IP Core Generator aracını kullanın.

Oluşturacağınız hafıza birimi 128 kelime kapasiteli 16-bitlik yazılabilir/okunabilir olmalıdır. Ayrıca .coe

uzantılı dosyayı kullanarak işlemcinin işleyeceği komutları hafıza birimine yazın.

4) Projenizde Resetn ve Run girişlerini buton ve anahtara bağlayın ve pin atamalarını gerçekleştirip FPGA

kartına göndererek işlemcinizin işlevselliğini kontrol edin.

Uygulama IV

Bu uygulamada bir öncekinde oluşturduğumuz işlemciye ek giriş çıkış aygıtları bağlayacağız. seg7_scroll

adında yeni bir modül oluşturacağız. Bu modül FPGA kartındaki her bir 7-parçalı gösterge için bir kaydedici

içermelidir. İşlemcinizin bu göstergeleri kullanabilmesi için her kaydedici direk olarak göstergelerdeki ledleri

kontrol etmelidir. Ayrıca işlemciniz bu kaydedicilere veri gönderebilmesi için yeni bir adres çözümleme devresi

oluşturulmalısınız.

1) Yeni bir ISE Design Suite projesi oluşturun.

2) Şekil-5’deki devreye ek olarak yeni oluşturacağınız seg7_scroll modülünün verilog kodunu oluşturun.

3) 7-parçalı göstergeleri kullanabilmek için yeni bir .coe uzantılı dosya oluşturun. Önce göstergelere bir

kelime yazan basit bir kod oluşturun ve daha sonra bu kodu yazılan kelimenin sağa ya da sola

kaymasını sağlayacak şekilde genişletin.

4) Projenizin pin atamalarını yaparak FPGA kartına yükleyip gerçekleyin.

Uygulama V

Bu uygulamada bir önceki uygulamaya port_n adında yeni bir modül ekleyeceğiz. Bu modül kartın

üzerindeki anahtarların o andaki durumlarını bir kaydediciye yazarak işlemcinin bu bilgiyi ld komutunu

kullanarak kullanmasını sağlayacaktır. Ayrıca işlemcinin bu bilgiye ulaşabilmesi için adres çözümlemesinde ek

devreye ve çoğullayıcıya ihtiyaç duyacaksınız.

1) Oluşturacağınız modülün işlemciyle iletişimini bir devre şeması ile gösterin.

2) Yeni bir proje oluşturun ve verilog kodlarını yazın. COE dosyanızı göstergelerdeki kelimenin kayma

hızını port_n modülünden okuduğu değere göre ayarlayacak şekilde uygulamayı ayarlayın.

3) Devrenizin davranışını simülasyon ve karta yükleyerek kontrol edin.