LABORATUVAR ÇALIŞMASI – 9

Basit İşlemci – I

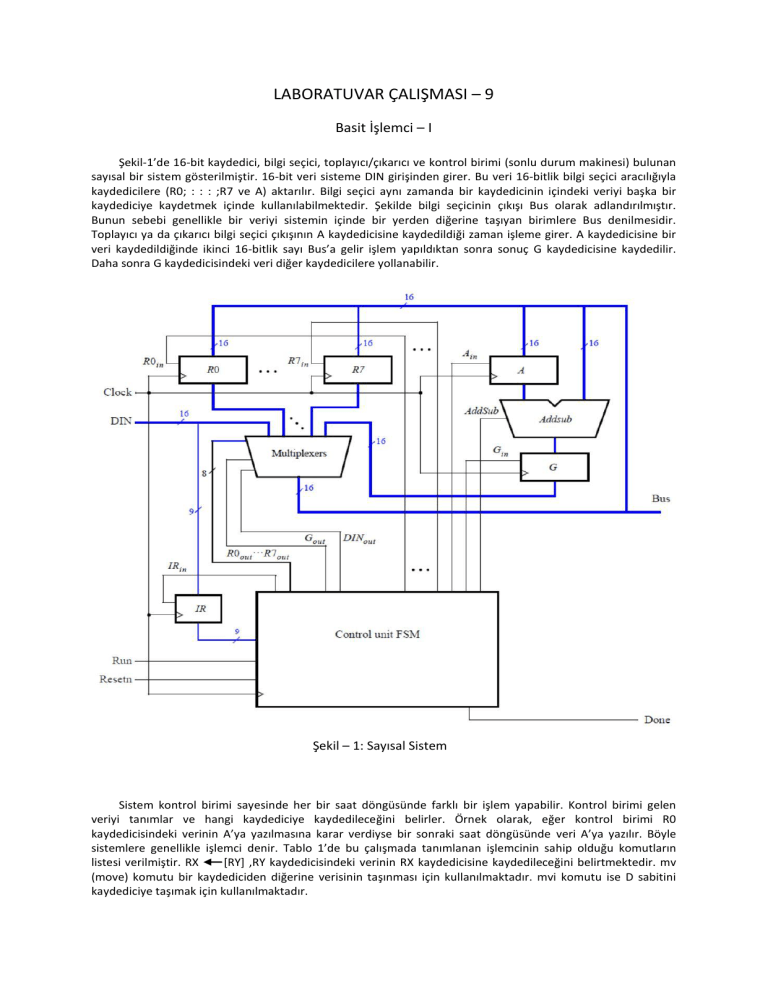

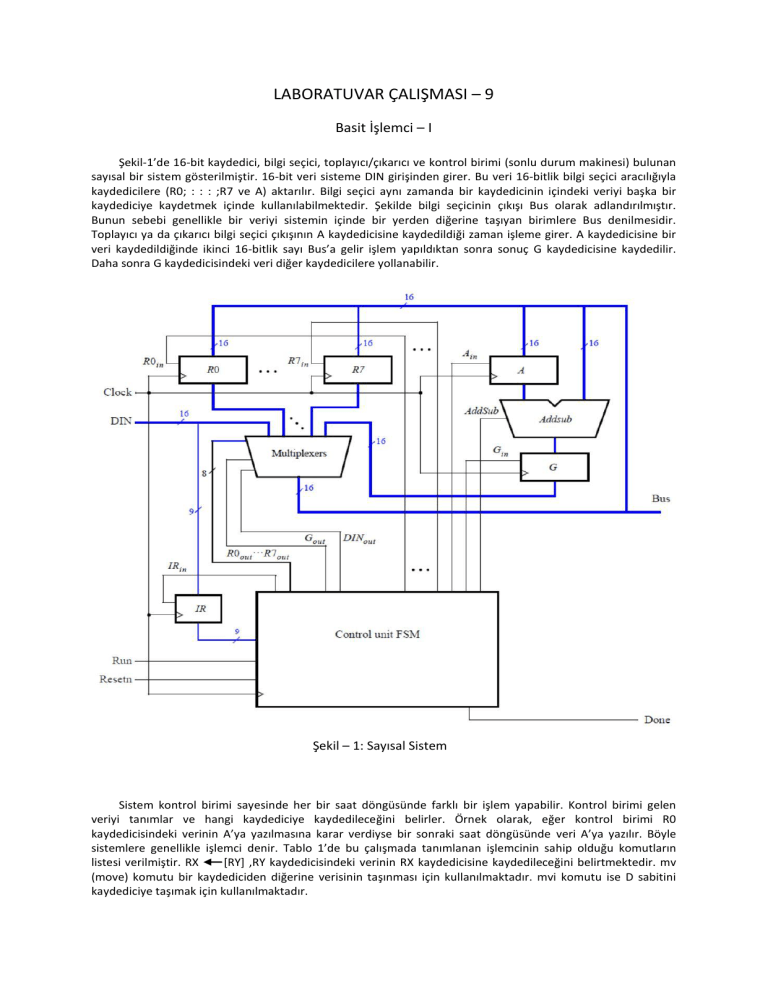

Şekil-1’de 16-bit kaydedici, bilgi seçici, toplayıcı/çıkarıcı ve kontrol birimi (sonlu durum makinesi) bulunan

sayısal bir sistem gösterilmiştir. 16-bit veri sisteme DIN girişinden girer. Bu veri 16-bitlik bilgi seçici aracılığıyla

kaydedicilere (R0; : : : ;R7 ve A) aktarılır. Bilgi seçici aynı zamanda bir kaydedicinin içindeki veriyi başka bir

kaydediciye kaydetmek içinde kullanılabilmektedir. Şekilde bilgi seçicinin çıkışı Bus olarak adlandırılmıştır.

Bunun sebebi genellikle bir veriyi sistemin içinde bir yerden diğerine taşıyan birimlere Bus denilmesidir.

Toplayıcı ya da çıkarıcı bilgi seçici çıkışının A kaydedicisine kaydedildiği zaman işleme girer. A kaydedicisine bir

veri kaydedildiğinde ikinci 16-bitlik sayı Bus’a gelir işlem yapıldıktan sonra sonuç G kaydedicisine kaydedilir.

Daha sonra G kaydedicisindeki veri diğer kaydedicilere yollanabilir.

Şekil – 1: Sayısal Sistem

Sistem kontrol birimi sayesinde her bir saat döngüsünde farklı bir işlem yapabilir. Kontrol birimi gelen

veriyi tanımlar ve hangi kaydediciye kaydedileceğini belirler. Örnek olarak, eğer kontrol birimi R0

kaydedicisindeki verinin A’ya yazılmasına karar verdiyse bir sonraki saat döngüsünde veri A’ya yazılır. Böyle

sistemlere genellikle işlemci denir. Tablo 1’de bu çalışmada tanımlanan işlemcinin sahip olduğu komutların

listesi verilmiştir. RX

[RY] ,RY kaydedicisindeki verinin RX kaydedicisine kaydedileceğini belirtmektedir. mv

(move) komutu bir kaydediciden diğerine verisinin taşınması için kullanılmaktadır. mvi komutu ise D sabitini

kaydediciye taşımak için kullanılmaktadır.

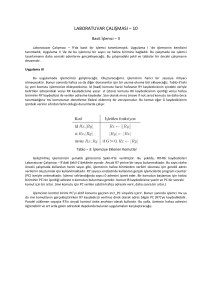

Tablo – 1: Komut Listesi

Her komut IR kaydedicisine 9-bitlik IIIXXXYYY şeklinde kodlanarak kaydedilir. Burada III kısmı komutun ne

olduğunu, XXX kısmı RX kaydedicisinin hangisi olduğunu, YYY kısmı ise RY kaydedicisinin hangisi olduğunu işaret

eder. Komut için 2-bitlik kod yeterli olmasına karşın işlemciye daha sonra başka komutlarda ekleyeceğimiz için

3-bit kulandık. Bu yüzden Şekil-1’de gösterildiği gibi DIN girişinin 9-biti IR kaydedicisine bağlanmıştır. mvi

komutu için YYY kodlarının bir anlamı yoktur ve mvi komutu IR kaydedicisine yazıldığında DIN girişine gelen 16bitlik veri işleme alınır.

Toplama ya da çıkarma gibi işlemi sırasında çoklu atama yapılan komutların tamamlanmaları için birden

çok saat döngüsüne ihtiyaç duyulur. Kontrol birimindeki sonlu durum makinesi bir sonraki komuta geçmeden

işlemdeki komutun tamamlanmasını sağlamak için saati kontrol etmektedir. İşlemci bir komutu işlerken Run

sinyali verilir ve komut tamamlandığında ise Done sinyali verilerek komutun bittiği haber verilir. Tablo-2’de

Tablo-1’deki komutların kontrol sinyalleri gösterilmiştir. Burada T0 anında IRin kontrol sinyali olmasına karşın

tabloda T0 anı verilmemiştir.

Tablo – 2: Komut Seti/Zaman İlişkisi

Uygulama I

Şekil-1’deki işlemciyi Verilog programlama dilini kullanarak aşağıdaki gibi tasarlayıp gerçekleyin:

1) Devreniz için bir ISE Design Suite projesi oluşturun.

2) İstenen Verilog dosyasını oluşturun, projenize ekleyin ve derleyin. Oluşturmanız gereken Verilog

kodunun iskelet yapısı Şekil-2’de verilmiştir.

3) Oluşturduğunuz Verilog kodu için ISim aracını kullanarak simülasyon yapınız ve simülasyon sonuçlarını

doğrulayınız.

4) Bir modül daha oluşturarak giriş ve çıkışları FPGA kartına uygun şekilde ayarlayın. SW15-0 anahtarlarını

DIN girişine, BTNL butonunu Run girişine, BTNR butonunu Resetn girişine ve BTNC butonunu da Clock

girişine bağlayın. Bus çıkışını LED15-0 ledlerine bağlayın.

5) Projenizin pin atamalarını yaparak FPGA kartında gerçekleyin.

Şekil – 2: İşlemci Verilog Kodu İskelet yapısı

Uygulama II

Bu uygulamada Şekil-3’teki gibi bir sayıcı ve bir hafıza birimi eklenmiş işlemciden oluşan devreyi

tasarlayacaksınız. Sayıcı hafıza biriminin adreslerini elde etmek için kullanılacak ve devrenizde PClock (işlemci

için) ve MClock (hafıza için) olmak üzere iki ayrı saat kullanılacaktır.

Şekil – 3: İşlemciye Hafıza ve Sayıcının Bağlanması

1) Yeni bir ISE Design Suite projesi oluşturun.

2) İşlemci, sayıcı ve hafıza birimini birleştiren bir Verilog dosyası oluşturun.

3) Hafıza birimi için IP Core Generator aracını kullanarak 16 bitlik 32 kelime kapasiteli bir ROM oluşturun.

İşlemcinin komutlarını hafıza birimine yazmak için ön tanımlı değerleri hafızaya kaydetmelisiniz. Bunun

için ROM oluştururken, komutların yazılı olduğu .coe uzantılı dosyayı Memory Initialization kısmına

yüklemeyi unutmayın. Örnek .coe uzantılı dosya için Xilinx firmasının internet adresini ziyaret

edebilirsiniz.

4) Simülasyonu çalıştırarak işlemciniz ile ROM devrenizin doğru haberleştiğinden emin olun.

5) Projenizin Run, Reset, PClock ve MClock girişlerini butonlara atayınız. Çıkışları ise göstergelerde

gözlemleyiniz.