BĠLEġĠMSEL DEVRELER (COMBĠNATIONAL)

ARĠTMETĠK ÜNĠTELER

Toplama, çıkarma,çarpma ve bölme gibi aritmetik iĢlemleri yapan sayısal devrelere aritmetik

devreler adı verilir. Sayısal sistemlerde temel aritmetik iĢlemler toplama ve çıkarma iĢlemidir.

Çarpma iĢlemi tekrarlanan toplama, bölme iĢlemi ise tekrarlanan çıkarma iĢlemi ile tanımlanır.

TOPLAYICI DEVRELER (ADDERS)

Sayısal devreler için toplama iĢlemini gerçekleĢtiren devrelere toplayıcılar (adders) adı verilir.

AĢağıda Binary (ikilik) sayıların toplamına iliĢkin temel kurallar verilmiĢtir.

0

0

1

1

+

+

+

+

Elde(Carry)

0=

0

1=

0

0=

0

1=

1

Sonuç(Sum)

0

1

1

0

Not: Toplama iĢlemi sonunda oluĢan eldenin iĢlem sonucunun en yüksek değerlikli

basamağı olduğu unutulmamalıdır.

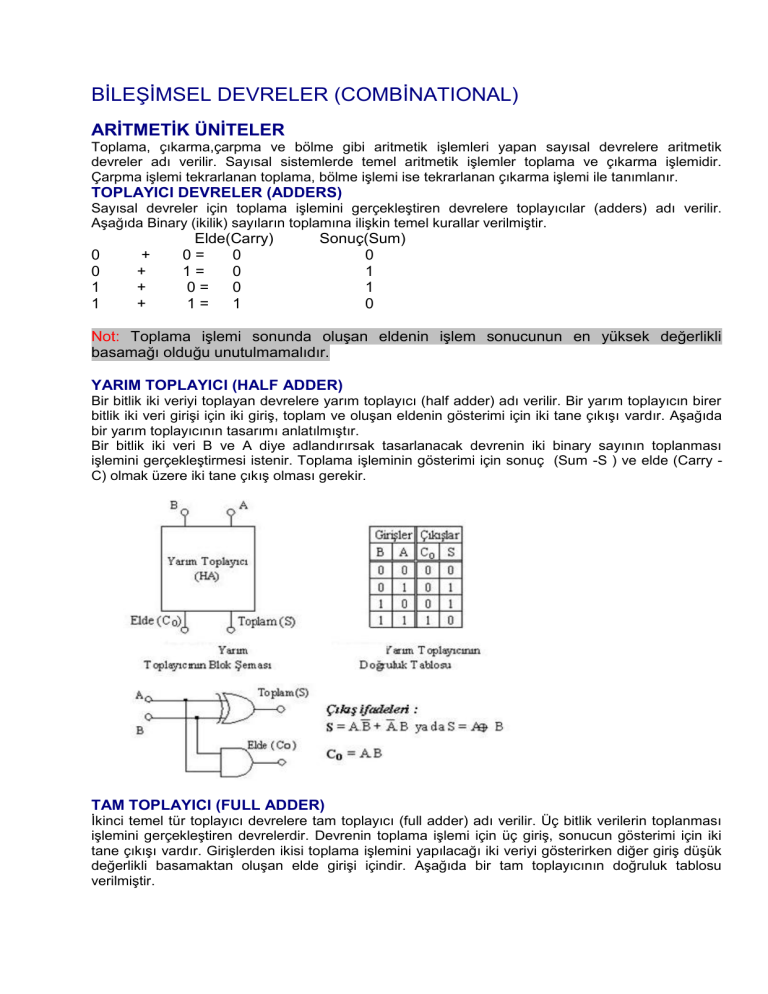

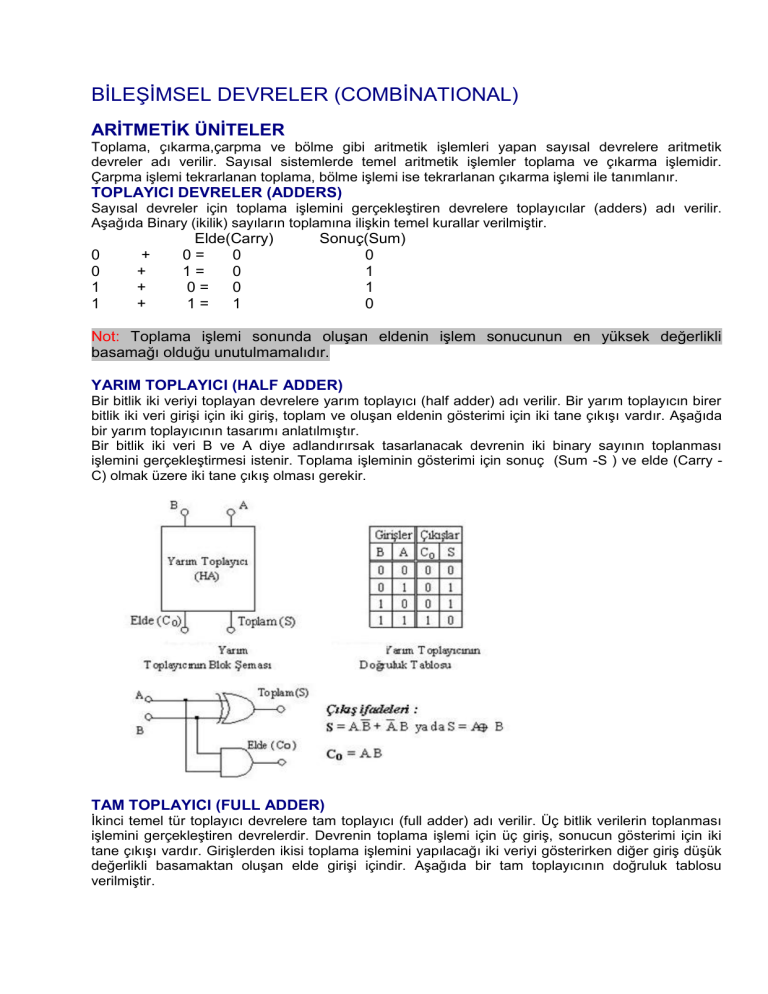

YARIM TOPLAYICI (HALF ADDER)

Bir bitlik iki veriyi toplayan devrelere yarım toplayıcı (half adder) adı verilir. Bir yarım toplayıcın birer

bitlik iki veri giriĢi için iki giriĢ, toplam ve oluĢan eldenin gösterimi için iki tane çıkıĢı vardır. AĢağıda

bir yarım toplayıcının tasarımı anlatılmıĢtır.

Bir bitlik iki veri B ve A diye adlandırırsak tasarlanacak devrenin iki binary sayının toplanması

iĢlemini gerçekleĢtirmesi istenir. Toplama iĢleminin gösterimi için sonuç (Sum -S ) ve elde (Carry C) olmak üzere iki tane çıkıĢ olması gerekir.

TAM TOPLAYICI (FULL ADDER)

Ġkinci temel tür toplayıcı devrelere tam toplayıcı (full adder) adı verilir. Üç bitlik verilerin toplanması

iĢlemini gerçekleĢtiren devrelerdir. Devrenin toplama iĢlemi için üç giriĢ, sonucun gösterimi için iki

tane çıkıĢı vardır. GiriĢlerden ikisi toplama iĢlemini yapılacağı iki veriyi gösterirken diğer giriĢ düĢük

değerlikli basamaktan oluĢan elde giriĢi içindir. AĢağıda bir tam toplayıcının doğruluk tablosu

verilmiĢtir.

SORU: Yarım toplayıcı ile tam toplayıcı arasındaki fark nedir?

Yarım toplayıcının elde giriĢi yoktur. Tam toplayıcının elde giriĢi vardır ve çok sayıda bitin

toplamında kullanılabilir.

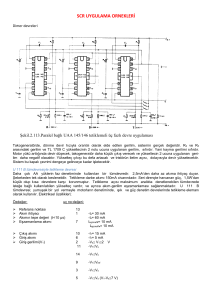

PARALEL TOPLAYICILAR (PARALLEL ADDERS)

Bir n-bitlik paralel toplayıcı n tane tam toplayıcının birbirine paralel bağlanması ile elde edilebilinir.

Her bir tam toplayıcının elde çıkıĢı (Cout) daha yüksek değerli toplayıcının elde giriĢine bağlanır.

Böylece düĢük değerlikli basamakların toplamından oluĢan elde (Cout) bir sonraki toplamı yapılacak

basamaklara etki edebilecektir.

Cin3

Cin2

Cin1

Cin

Toplamlara ait çıkıĢ ifadeleri:

A3

A2

A1

Ao

So= Cin+ Ao+B0

S1= Cin1+ A1+B1

+

B3

B2

B1

Bo

S2= Cin2+ A2+B2

S3= Cin3+ A3+B3

Cout

S3

S2

S1

S0

KARġILAġTIRICILAR( COMPARATORS)

KarĢılaĢtırma iĢlemi giriĢindeki sayısal bilgilerden birinin diğerine göre büyük, küçük veya eĢit olma

durumlarının belirlenmesidir.

En temel karĢılaĢtırıcı devreleri Özel-Veya (Xor) kapılarıdır. Bir Özel-Veya kapısının giriĢleri farklı

iken çıkıĢ Lojik-1,giriĢleri aynı iken çıkıĢ Lojik-0‟dır.

Örnek:

Bir bitlik A ve B verilerini karĢılaĢtıran bu karĢılaĢtırma sonunda A>B,

gösteren devreyi tasarlayınız.

Devreye ait doğruluk tablosu aĢağıdaki gibi olacaktır.

A=B,

A<B durumlarını

ENCODER (KODLAYICILAR)

Kodlayıcı devre (encoder circuit ) kod çözücü devrenin tersi iĢlemi yapar. Bu devreler, decimal veya

bilinen klasik Ģekillerdeki bilgileri sayısal devrelerin iĢlem yapabileceği Ģekle dönüĢtürürler. Bir

kodlayıcının (encoder) 2n (yada daha az) giriĢ hattı ve n sayıda çıkıĢ hattı üretir.

DECĠMAL-BCD ENCODER

Decimal – BCD encoder giriĢindeki decimal bilgiyi kodlayarak BCD kod karĢılığını dört çıkıĢta

gösterir. AĢağıda 10x4 encoder lojik sembolü ve doğruluk tablosu verilmiĢtir.

ÇıkıĢları Lojik ifade doğruluk tablosundan yazmak istersek;

A3 = D8 + D9

A2 = D4 + D5 + D6 + D7

A1 = D2 + D3 + D6 + D7

A0 = D1 + D3 + D5 + D7 + D9

AĢağıda Decimal-BCD Encoder‟ in Lojik diyagramı verilmiĢtir.

KOD ÇÖZÜCÜLER(DECODERS)

Sayısal sistemlerde bilgiler ikilik kodlarla tanımlanırlar. n bitlik bir ikilik kod ile 2 n kadar farklı durum

tanımlanabilir. Bir kod çözücü, n giriĢ hattından gelen ikilik bilgileri maximum 2n kadar farklı çıkıĢ

hattına dönüĢtüren birleĢik bir devredir. Bir kod çözücünün n kadar giriĢi varsa 2n kadar çıkıĢı vardır.

Kullanılmayan veya dikkate alınmaz durumlar varsa kod çözücü çıkıĢı 2n‟ den az olacaktır.

ĠKĠ GĠRĠġLĠ KOD ÇÖZÜCÜ

Ġki bitlik bir kod çözücünün 2 giriĢi 4 çıkıĢı vardır. Böyle bir devre için giriĢlerin durumuna bağlı olarak

sadece tek bir çıkıĢ doğru olacaktır. AĢağıda 2x4 Kod çözücünün doğruluk tablosu ,Lojik diyagramı

ve sembolü verilmiĢtir.

ĠKĠ BĠTLĠK KOD ÇÖZÜCÜ

ÜÇ GĠRĠġLĠ KOD ÇÖZÜCÜ

Üç bitlik kod çözücüde(decoder) üç giriĢin kodu çözülerek sekiz çıkıĢ üretir. Her çıkıĢ bu üç giriĢ

değiĢkenine ait bir minimum terimle tanımlanır. GiriĢlerin durumuna bağlı olarak sadece tek bir çıkıĢı

doğrudur.

ÜÇ BĠTLĠK KOD ÇÖZÜCÜ

YETKĠ GĠRĠġLĠ KOD ÇÖZÜCÜLER

Kod çözücülerin tamamı olmasada büyük bir bölümü bir veya birden çok yetki (enable) giriĢi içerir.

Kod çözücü (decoder) sadece yetkilendiğinde (enable giriĢine gelen Lojik-1 veya Lojik-0 ) kod

çözme iĢlemini gerçekleĢtirir. Diğer bütün durumlarda kod çözücü (decoder) çıkıĢları Lojik-1 veya

Lojik-0 olur.

Not: Yetkilendirme, çalıĢılan decoder özelliğine göre Lojik-1 veya Lojik-0 da olabilir.

BCD DECĠMAL KOD ÇÖZÜCÜ

BCD kodu 0 – 9 arasındaki Decimal(Onluk) sayıların 4-Bitlik Binary(Ġkilik) karĢılıklarının yazılması ile

tanımlanmıĢ bir kodlamadır. Bu durumda tasarlanacak kod çözücünün 4 giriĢ hattı olması, BCD

kodu 0-9 arasındaki Decimal(Onluk) sayılar arasında tanımlı olduğundan 10 çıkıĢ hattının olması

gerekmektedir. Geri kalan durumlar don’t care (dikkate alınmaz durumlar) olarak tanımlanacaktır.

BCD SEVEN SEGMENT KOD ÇÖZÜCÜ

Yedi ayrı Led‟in uygun bağlanması ile 0-9 arasındaki sayıları görüntüleyebiliriz. Bu iĢlemi yapan

devre elemanına yedi parçalı gösterge(seven segment display) adı verilir. Display led bağlantılarına

göre ortak anot veya ortak katot‟lu olabilir.

7 Segment Display

Ortak anotlu display

Ortak katotlu display

AĢağıda Ortak Katotlu Display için BCD- Seven Segment Decoder doğruluk tablosu verilmiĢtir.

MULTĠPLEXERS (DATA SELECTORS-ÇOĞULLAYICILAR-VERĠ

SEÇĠCĠLER)

Çoğullama çok sayıdaki bilginin,daha az sayıda kanal veya hat üzerinden iletilmesi anlamına gelir.

Sayısal çoğullayıcı, birçok giriĢ hattının birisinden gelen ikilik bilgileri seçen ve tekbir çıkıĢ hattına

yönlendiren birleĢik bir devredir. Belli bir giriĢin seçilmesi bir dizi seçme hattı ile kontrol edilir. Bir

n

çoğullayıcı için 2 sayıda giriĢ hattı varsa hangi giriĢin seçileceğini belirleyen n kadar seçme

hattı vardır. Örneğin 4 giriĢ varsa en az iki seçme ucu gerekir.

Buna en iyi örnek bir stüdyodaki kameraların hangisinin görüntüsünün izleyiciye gönderileceğini

belirleyen devrelerdir. Çok sayıda kameranın hangisini görüntüsünün yansıtılacağı multiplexer

devreleriyle belirlenir.

Çok sayıda giriĢi tek çıkıĢı vardır. ÇıkıĢa hangi giriĢ bilgisinin gönderileceği seçme uçlarıyla

belirlenir.

Bazı durumlarda kod çözücülerde olduğu gibi Multiplexler içinde çalıĢmayı kontrol eden bir

yetkilendirme (enable) giriĢi bulunabilir.

DEMULTIPLEXLER (BĠLGĠ DAĞITICILAR-DATA DISTRIBUTORS)

Demultiplexer (Bilgi Dağıtıcı) tek bir hattan bilgi alan ve bu bilgiyi olası 2n sayıda çıkıĢ hattından birisi

üzerinden ileten bir devredir. Belli bir çıkıĢ hattının Ģeçimi n kadar çıkıĢ hattının durumları tarafından

kontrol edilir. Tek giriĢi çok sayıda çıkıĢı vardır. GiriĢteki bilginin hangi çıkıĢa yansıyacağı seçme

uçlarıyla belirlenir.

AĢağıda iki seçme hattı ve dört çıkıĢ hattı olan bir DEMUX‟ un doğruluk tablosu ve lojik sembolü

verilmektedir.

MULTĠVĠBRATÖRLER

Sayısal devrelerde tetikleme sinyali olarak kullanılan kare,dikdörtgen sinyali üreten devrelere

multivibratör (osilatör) adı verilir. Multivibratörler üç grupta incelenirler.

I. Tek kararlı (Monostable) multivibratörler,

II. Kararsız (Astable) multivibratörler,

III. Çift kararlı (Bistable) multivibratörler.

MONOSTABLE (TEK KARARLI) MULTĠVĠBRATÖRLER

Monostable multivibratörler giriĢlerine uygulanan iĢarete bağlı olarak sadece tek bir darbe Ģeklinde

çıkıĢ iĢareti verirler. ÇıkıĢiĢaretinin süresi, dıĢarıdan bağlanacak olan zamanlama (direnç ve

kondansatör) elemanlarının değerlerine bağlıdır.

Yandaki Ģekilde transistörlü monostable

multivibratör

devresini

görülmektedir.

BaĢlangıçta R1 direnci üzerinden beyz

polarması alan T1 transistörü iletimde,T2

transistörü kesimdedir. Bu sırada C

kondansatörü Ģarj olacaktır. Tetikleme

giriĢinden pozitif bir tetikleme sinyali

verildiği anda T2 transistörü iletime

geçecek, C kondansatörü R1 ve T2

transistörü üzerinden deĢarj olacak ve

beyz polarması alamayan T1 transistörü

kesime gidecektir. Bir sonraki tetikleme

sinyaline kadar bu durum sürecektir.

KARARSIZ (ASTABLE) MULTĠVĠBRATÖRLER:

Bir diğer tür multivibrator devresi astable (kararsız) multivibrator adını alır. ÇalıĢma gerilimi

uygulandığı andan itibaren zamanlama elemanlarının belirlediği sürelerde durum değiĢtiren

devrelerdir. Astable multivibrator zamanlama devrelerinde tetikleme sinyali amaçlı bir kare dalga

osilatör olarak kullanılırlar.

ġekilde transistorlü astable multivibrator

devresi görülmektedir. Devrede birbirine

simetrik bağlı iki npn transistör vardır.

Devredeki elemanlar T1=T2, C1=C2,

Rc1=Rc2 ve R1=R2 seçilse bile, gerilim

uygulandığı zaman transistorlerden biri

iletimde diğeri kesimde olacaktır. Enerji

verildiğinde T1 transistörünün kesim ve T2

transistörünün iletimde olduğunu kabul

edelim. Bu anda C1 kondansatörü deĢarj

ve C2 Ģarj olmuĢ durumdadır. Bundan

sonra C1 kondansatörü RC1 direnci

üzerinden Ģarja, C2 kondansatörü R2

direnci üzerinden deĢarja baĢlayacaktır. Bir süre sonra C2 kondansatörü T1 transistörünü iletime

sokacak Ģekilde deĢarj , C1 kondansatörü T2 transistörünü kesime götürecek Ģekilde Ģarj olacaktır.

T1 transistörü doyuma, T2 transistörü kesime gidecektir. Bu andan sonra C1 kondansatörü R1

direnci üzerinden deĢarja ve C2 kondansatörü RC2 direnci üzerinden Ģarja baĢlayacaktır. Bir süre

sonra C1 kondansatörü T2 transistörünü doyuma götürecek Ģekilde deĢarj , C2 kondansatörü T1

transistörünü iletime sokacak Ģekilde Ģarj olacaktır.

Transistorlerin iletimde olma süreleri kondansatörlerin deĢarj sürelerine bağlıdır. Yani T1 transistörü

R2-C2 , T2 transistörü R1-C1 zamanlama elemanlarının belirlediği sürelerde kesimde ve doyumda

olacaktır.

ÇĠFT KARARLI (BĠSTABLE) MULTĠVĠBRATÖRLER

DıĢarıdan bir tetikleme sinyali gelmediği müddetçe durumlarını koruyan devrelere çift kararlı

(bistable) multivibrator adı verilir. DıĢarıdan uygulanan her tetikleme sinyalinde devre konum

değiĢtirecektir.

ġekil transistörlü bistable multivibrator

devresini

göstermektedir.

Devrede

birbirine simetrik bağlı iki npn transistör

vardır. Devredeki elemanlar T1=T2,

Rc1=Rc2,R1=R2 ve R3=R4 seçilse bile ,

güç uygulandığı zaman transistorlerden

biri iletimde diğeri kesimde olacaktır.

Devrenin çalıĢmasını açıklamak için güç

verildiği anda T1 transistörünün doyumda,

T2 transistörünün kesimde olduğunu kabul

edelim. Budurumda Q=1 ve Q = 0 durumu

çıkıĢlarda görülecektir. Devreye bir

tetikleme sinyali gelmediği müddetçe

transistorler bu durumlarını koruyacaktır.

Devrenin konumunu değiĢtirmek için S1 anahtarına basıp T1 transistörünün beyzine negatif bir

tetikleme sinyali verilirse (ġekil 7.15 b), bu durumda T1 transistörü kesime,T2 transistörü doyuma

geçecektir. Bu durumda çıkıĢlar Q=0 ve Q =1 olacaktır. Bir sonraki tetikleme sinyaline kadar çıkıĢlar

bu durumlarını koruyacaktır. Devrenin konumunu değiĢtirmek için S2 anahtarına basılırsa, T2

transistörünün beyzine negatif tetikleme sinyali uygulanır. Bu durumda T2 transistörü kesime,T1

transistörü doyuma gideceğinden çıkıĢlar konum değiĢtirecek, Q=1 ve Q = 0 olacaktır.

Devrenin durumunu değiĢtirecek olan tetikleme giriĢi o an doyumda olan transistorün beyzine bağlı

olan giriĢtir. Çift kararlı multivibratör devreleri “ Flip-Flop ” olarak adlandırılır. Ve sayıcı

devreleri,kaydedici devreleri, bellek devreleri gibi uygulama alanlarında sıklıkla kullanılırlar.

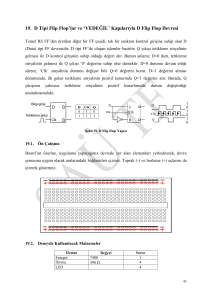

FLİP-FLOPLAR:

GiriĢlerine uygulanan sinyal ile çıkıĢları iki kararlı olan elektronik elemanlardır. GiriĢlerine uygulanan

sinyal değiĢtirilmediği sürece çıkıĢ durumunu korurlar ve bir bitlik bilgiyi saklarlar. GiriĢ sinyaline göre

çıkıĢ lojik-1 veya lojik-0 olur.

BaĢlıca Flip-Flop çeĢitleri Ģunlardır:

1-) RS FF

2-) JK FF

3-) D FF

4-) T FF

1-) RS FF: R (Reset=sıfırla) ve S (Set=kur) olmak üzere iki giriĢe sahiptir. Q ve

çıkıĢı vardır.

olmak üzere iki

*

RS FF un doğruluk tablosu

RS FF un lojik diyagramı

* Ġstenmeyen durum (S ve R giriĢlerinin aynı anda 1 olması istenmez. ÇıkıĢ kararsız olur.)

TETĠKLEMELĠ RS FF: Temel bir FF devresinin giriĢine kapı eklemek suretiyle FF un çıkıĢının harici

bir saat darbesi (clock pulse- CK) ile giriĢlerin değiĢimine tepki vermesi sağlanabilir. Flip-Flopların bu

anlık değiĢimine tetiklenme adı verilir. Ve bu değiĢimi sağlayan duruma ise flip-flop‟un tetiklenmesi

denir.

Buradaki CK (Clock) giriĢi tetikleme sinyalini gireceğimiz yerdir. Bu giriĢten kare dalga uygulanır.

Flip-flobun çıkıĢlarının değiĢebilmesi için bu kare dalgaya ihtiyaç vardır. R ve S giriĢleri değiĢmiĢ

olsalar dahi kare dalganın palsi gelmeden çıkıĢ konum değiĢtirmez. R ve S değiĢtiğinde flip flop

çıkıĢlarını değiĢtirmek için hazır bekler.

JK FF:

RS FF‟lerde R=1 ve S=1 olduğunda belirsizlik durumu oluĢur ve bu giriĢlerin

kullanılmaması gerekebilir. ĠĢte bu durumu yok etmek için RS FF geliĢtirilerek JK, D ve T flip floplar

bulunmuĢtur. Bu flip floplarda belirsizlik durumu yoktur.

D FF: Tek giriĢi vardır. D (Data) tipi flip flop, bilgi kaydetmede kullanılan bir flip flopdur ve genellikle

kaydedici devrelerinde kullanılır. D tipi flip flop, JK tipi flip floba bir “DEĞĠL” kapısı eklenip giriĢleri

birleĢtirilerek elde edilir. D tipi flip flopda giriĢ ne ise, her gelen tetikleme palsi ile çıkıĢ o olur.

T FF: T

flip flop, JK flip flobun giriĢ uçları kısa devre edilerek tek giriĢli hale getirilmiĢ Ģeklidir. O

yüzden T FF entegresi yerine, JK FF entegresi alınıp giriĢleri kısa devre edilerek T FF entegresi

yapılabilir. Zaten piyasada T flip flop yerine, JK flip flop kullanılmaktadır.

NOT: FF ların lojik kapı eĢdeğer devreleri, doğruluk tabloları ve geçiĢ tabloları ezberlenmeyecek. Sınav

kağıdında gerekli bilgiler verilecektir.

FF GEÇĠġ TABLOLARI

Tasarım yaparken FF geçiĢ tablolarından yararlanılır.

FF LARIN TETĠKLENMESĠ:

Bilindiği gibi tetiklemeli FF larda sadece giriĢlerin değiĢmesi çıkıĢın değiĢmesi için yeterli değildir.

Clock palsinin de gelmesi gerekir.

PRESET-CLEAR GĠRĠġLĠ FF LAR:

Preset=ön kurma ve clear=temizle anlamındadır. Ön kurma, üst seviye kurma anlamındadır. Daha

önce set (kurma) iĢleminin ne demek olduğunu RS FF‟leri incelerken görmüĢtük. Kurma, çıkıĢı “1”

yapma anlamına gelmekteydi. PR giriĢi de çıkıĢı “1” yapan giriĢtir. Diğerinden farkı daha üst bir

yetkiye sahip olmasıdır. CLR giriĢi ise, aynı reset giriĢinde olduğu gibi, çıkıĢı temizleyen yani “0”

yapan giriĢtir.

Burada preset ve clear giriĢlerindeki yuvarlak semboller bu

giriĢlerin lojik „0‟ ile aktif hale geldiğini gösterir. Yani clear

giriĢini „0‟ yaparsak giriĢler ne olursa olsun çıkıĢ „0‟; preset

giriĢini „0‟ yaparsak giriĢler ne olursa olsun çıkıĢ „1‟ olur.

Örnek: AĢağıda giriĢ ve clock sinyalleri verilen FF ların çıkıĢ sinyallerini çiziniz.

(COUNTERS) SAYICILAR

GiriĢ darbelerine bağlı olarak belirli bir durum dizisini tekrarlayan devrelere sayıcı (counters) adı

verilir. GeniĢ bir uygulama alanı bulan sayıcı devreleri zamanlama (frekans bölme vb.) ve kontrol

(kodlama, bilgi depolama vb.) devrelerinde kullanılmaktadır. Genel olarak sayıcı devrelerini

aĢağıdaki gibi sınıflandırabiliriz.

a- Tetikleme sinyalinin uygulanmasına göre

I. Asenkron Sayıcılar II. Senkron Sayıcılar

b- Sayma yönüne göre

I. Yukarı – Ġleri Sayıcılar (Up Counters)

II. AĢağı – Geri Sayıcılar (Down Counters)

III. Yukarı / AĢağı Sayıcılar (Up / Down Conters )

c- Elde edilen sayının kodlanmasına göre

I. Ġkilik Sayıcı (Binary Counter)

II. BCD Sayıcı (BCD Counter)

III. Onluk Sayıcı (Decimal Counter)

Bir sayıcının tekrar yapmadan alabildiği durum sayısına veya sayabildiği sayı miktarına o sayıcının “

mod” „u adı verilir. Örneğin Mod-13 sayıcı tekrar yapmadan onüç değiĢik durum alabilir. Yani Mod13 sayıcı 0-12 arası sayıları sayacak ve tekrar 0‟a dönecektir.

ASENKRON SAYICILAR (ASYNCHROUNS COUNTERS)

Bu tip sayıcılarda flip-flop‟ların tetikleme sinyali bir önceki flip-flop çıkıĢlarından alınır. Asenkron

sayıcılarda FF lar aynı zamanda konum değiĢtirmez. Genellikle T FF vey JK FF kullanılır.

1-Asenkron Yukarı Sayıcılar (Asynchrouns Up Counters):

Asenkron yukarı sayıcı tasarlarken;

En düĢük değerlikli bite ait FF ilk sırada yer alır. Bu FF a dıĢarıdan clock sinyali uygulanır. ÇıkıĢ Q

çıkıĢlarından alınır. Sinyaller çizilirken de en üstte clock sinyali yer alır. Bundan sonra en düĢük

değerli bitten baĢlayarak sırasıyla FF çıkıĢlarına ait sinyaller çizilir.

1-Flip-Flop pozitif kenar tetiklemeli ise en düĢük değerlikli biti taĢıyan Flip-Flop hariç diğer bütün

Flip-Flop’ların tetikleme sinyali bir önceki Flip-Flop’un Q çıkışından alınır.

2-Flip-Flop düĢen kenar tetiklemeli ise en düĢük değerlikli biti taĢıyan Flip-Flop hariç diğer bütün

Flip-Flop’ ların tetikleme sinyali bir önceki Flip-Flop’ un Q çıkıĢından alınır.

Örnek:Negatif kenar tetiklemeli JK FF la 2 bitlik asenkron yukarı sayıcı tasarlayınız.

Ġki bitlik sayıcı en fazla (11)2=(3)10 a kadar sayar. Ġki FF kullanılacaktır. FF lar negatif kenar

tetiklemeli olduğu için ilk FF hariç diğerlerinin clock giriĢi bir önceki FF un Q çıkıĢından alınır. JK FF

un doğruluk tablosuna bakıldığında J ve K giriĢlerine aynı anda lojik „1‟ uygulanırsa çıkıĢ Q olur.

Yani FF çıkıĢı her clock palsi geldiğinde konum değiĢtirecektir.

Clock palsinin uygulandığı bit en değersiz bittir. Sıralama en önemsiz bitten en önemli bite doğru

yapılır.

0.Clock palsi uygulandığında FF0 konum değiĢtirir. FF1 etkilenmez. Yani J0=1 ve K0=1 olduğunda Q0

konum değiĢtirerek „0‟ dan „1‟e geçer.

1.clock palsi uygulandığında FF0 yine konum değiĢtirir, Q0 „1‟ den „0‟ a geçer. FF1 e de clock palsi

geldiğinden FF1 de konum değiĢtirir. Q1 konum değiĢtirerek „0‟ dan „1‟e geçer.

2. clock palsi uygulandığında FF0 konum değiĢtirir, FF1 etkilenmez.

3. clock palsi uygulandığında FF0 konum değiĢtirerek Q0 „0‟ dan „1‟e geçer. FF1 e gelen clock palsi

negatif kenar tetiklemesi olmadığından FF1 konum değiĢtirmez, Q1 „1‟ olarak kalır.

Örnek: JK FF larla 4 bitlik asenkron ileri sayıcı doğruluk tablosu, devresi ve çıkıĢ dalga Ģekilleri?

Önce 4 bitlik ileri sayıcının doğruluk tablosunu hazırlıyoruz. ÇıkıĢlarımız Q 3, Q2, Q1, Q0 olur. Ġlk FF a

clock palsi dıĢarıdan uygulanır. Diğerlerine ise clock palsi bir önceki FF un Q çıkıĢından alınır. (FF

negatif kenar tetiklemeli olduğundan) ÇıkıĢlar ise Q çıkıĢından alınır.

2-Asenkron Geri Sayıcılar (Asynchrouns Down Counters):

Asenkron aĢağı sayıcı tasarlarken;

I-Flip-Flop yükselen kenar tetiklemeli ise en düĢük değerlikli biti taĢıyan Flip-Flop hariç diğer bütün

Flip-Flop’ ların tetikleme sinyali bir önceki Flip-Flop’un Q çıkışından alınır.

II- Flip-Flop düĢen kenar tetiklemeli ise en düĢük değerlikli biti taĢıyan Flip-Flop hariç diğer bütün

Flip-Flop’ ların tetikleme sinyali bir önceki Flip-Flop’ un

’ çıkışından alınır.

Örnek: Ġki bitlik asenkron geri sayıcı, doğruluk tablosu ve dalga Ģekilleri.

0.Clock palsi uygulandığında FF0 ve FF1 konum değiĢtirir. Çünkü FF0 konum değiĢtirerek Q0 „0‟ dan

„1‟e geçerken

0 „1‟ den „0‟ a geçer. Bu sırada negatif tetikleme palsi oluĢacağından FF1

tetiklenir.

1.clock palsi uygulandığında FF0 yine konum değiĢtirir, Q0 „1‟ den „0‟ a geçer. FF0 ın değillenmiĢ

çıkıĢı ise „0‟ dan „1‟e geçeceğinden negatif kenar tetikleme palsi oluĢmaz ve FF1 konum değiĢtirmez.

2. clock palsi uygulandığında FF0 konum değiĢtirerek „0‟ dan „1‟e geçer. FF0 ın değillenmiĢ çıkıĢı ise

„1‟ den „0‟a geçeceğinden negatif kenar tetikleme palsi oluĢur ve FF1 konum değiĢtirir.

3. clock palsi uygulandığında FF0 yine konum değiĢtirir. FF1 etkilenmez.

MODLU (RESETLEMELĠ) ASENKRON ĠLERĠ VE GERĠ SAYICILAR:

Clock palsi sadece ilk FF a uygulanan, her birinin çıkıĢı bir sonraki FF un clock giriĢine bağlanan ve

çıkıĢlarından silme veya sıfırlama ucuna geri besleme yapılarak sayma sayısı sınırlanan sayıcılardır.

Modun hangi değerde olması isteniyorsa bu sayının Binary (ikilik) karĢılığı alınır. Sayıcı çıkıĢındaki

bit ağırlıkları dikkate alınarak uygun çıkıĢlar (lojik-1) bir VEDEĞĠL (NAND) kapısına girilir. Kapı çıkıĢı

sayıcı devresinin silme uçlarına uygulanır. AĢağıdaki Ģekildeki devre MOD 10 olarak ayarlanmıĢtır.

10 un ikilik karĢılığı 1010 olduğuna göre Q0=0, Q1=1, Q2=0 ve Q3=1 olur. Q3 ve Q1 aynı anda bir

olduğunda sayıcı 10 u saymadan sıfırlanır. (0,1,2,3,4,5,6,7,8,9) sayar ve baĢa döner.

SENKRON SAYICILAR (SYNCHROUNS COUNTERS)

Clock giriĢleri birleĢtirilerek aynı anda tetiklenen, sayma sırası tasarıma bağlı olarak değiĢebilen

sayıcılara denir. Tetikleme sinyalinin bütün Flip-Flop‟ların CLK giriĢlerine uygulanması açından

Asenkron sayıcılardan farklılık gösterir.

Senkron sayıcının tasarımı için iĢlem basamakları:

1- FF ların alacağı çıkıĢ değerleri tablo Ģeklinde düzenlenir.

2- Her bir çıkıĢın clock palsinden sonra alacağı yeni değer, Q+ olarak tabloya kaydedilir.

3- Tasarımda kullanılacak FF a ait geçiĢ tablolarından her bir çıkıĢın clock palsinden sonra

alacağı değere göre geçiĢ tablosu düzenlenir.

4- GeçiĢ tablosundaki her bir giriĢ Karnaugh haritasına aktarılır ve çıkıĢ ifadesi yazılır.

5- ÇıkıĢ ifadelerine göre devre Ģeması çizilir.

Örnek:Ġki bitlik senkron ileri sayıcının JK FF kullanılarak tasarımı

ÇÖZÜM:1- FF ların alacağı çıkıĢ değerleri tablo halinde düzenlenir.

2- Her bir çıkıĢın clock palsinden sonra alacağı yeni değer Q+ olarak tabloya kaydedilir.

Q1 in clocktan sonra alacağı değer Q1+, Q0 in

clocktan sonra alacağı değer Q0+ olarak

alınmıĢtır. Buna göre Q1+ yazılırken Q1

sütununda Q1 in hemen altındaki değer Q1+

olarak yazılır.

3- JK FF a ait geçiĢ tablosundan her bir çıkıĢın clock palsinden sonra alacağı değere göre geçiĢ

tablosu düzenlenir.

Q1 sütununda „0‟ ın altında „0‟ olduğundan 0. Satırda Q1+ „0‟ olur. JK FF geçiĢ tablosunda „0‟ dan „0‟

a geçiĢte J=0 ve K=X olduğu görülür. (X: 0 veya 1 olması fark etmez demektir.)

1.Satırda „0‟ olan Q1 altında „1‟ olduğundan Q1+ 1. Satıra „1‟ olarak yazılır. „0‟ dan „1‟ e geçiĢte J=1

ve K=X olduğu görülür.

2. satırdaki „1‟ olan Q1 altında „1‟ olduğundan „1‟ olduğundan Q1+ 2. Satıra „1‟ olarak yazılır. „1‟ dan

„1‟ e geçiĢte J=X ve K=0 olduğu görülür.

3.satırdaki „0‟ olan Q1 devamında baĢa döneceği için ilk satırda „0‟ olduğundan Q1+ 3. Satıra „0‟

olarak yazılır. „0‟ dan „0‟ e geçiĢte J=0 ve K=X olduğu görülür.

Q0+ sütunuda aynı yöntemle doldurulur.

4- GeçiĢ tablosundaki her bir giriĢ Karnaugh haritasına aktarılır ve çıkıĢ ifadeleri yazılır.

5-çıkıĢ ifadelerine göre devre Ģeması çizilir.

Örnek: Üç bitlik senkron ileri sayıcının JK FF kullanılarak tasarımı

FF ların alacağı çıkıĢ değerleri tablo Ģeklinde düzenlenir.

Senkron geriye sayıcı da aynı Ģekilde tasarlanır.

ĠSTENEN SIRAYA GÖRE SAYAN SENKRON SAYICININ TASARLANMASI:

Tablodaki sıraya göre çıkıĢ verecek sayıcıyı JK FF kullanarak tasarlayın.

ÇÖZÜM:

Yandaki tablodaki sıraya göre çıkıĢ verecek sayıcıyı T FF kullanarak

tasarlayınız

ÇÖZÜM: Karnaugh Haritalarında 0,1 ve X dıĢında boĢ kalan yerler B ile doldurulabilir. B, tıpkı X gibi

0 veya 1 olarak alınabilir.

ÖRNEK: Bir üretim bandında 3 ayrı motor çalıĢmaktadır. Önce tek tek sırasıyla 2. Motor, 1. Motor ve

0. Motor çalıĢıyor. Devamında bütün motorlar duruyor. Sonra bütün motorlar çalıĢıyor. Tekrar ilk

pozisyondan döngüye giriyor. Bu devreyi JK FF kullanarak tasarlayınız.

CLK

KAYDEDİCİLER (REGİSTERS):

Sayısal bilgileri geçici bir süre saklayan devrelere kaydediciler ( Registers) adı verilir. Bilginin

saklanması için kaydedicilerde her bir bitlik bilgi için bir adet flip-flop kullanılmaktadır. Bilginin

iĢlenmesi tetikleme sinyali (Clock pulse) ile senkron olarak yapılır. Kaydediciler besleme olduğu

sürece bilgiyi tutar, besleme kesildiğinde ise bilgiyi kaybederler.

Ġkilik sayı bitleri (veriler) kaydedilirken, iki yöntem kullanılır. Bunlardan ilki, sayıları flip flop sisteminin

giriĢine tek tek her saat sinyali ile kaydetmek. Bu iĢlem için sekiz bitlik sayıyı kaydetmek için 8 saat

sinyali kullanılır. Bu iĢleme seri veri giriĢi denir. Bir diğer yöntemde 8 flip flopun giriĢine bilgilerin

tamamını hazırlayıp tek saat sinyali ile kaydetmektir. Bu iĢlemede paralel veri giriĢi denir.

Bilgi giriĢ-çıkıĢına göre

I. Seri giriĢ- Seri çıkıĢlı kaydedici (Serial in- Serial out-SISO)

II. Seri giriĢ- Paralel ÇıkıĢlı kaydedici (Serial in- Parallel out- SIPO)

III. paralel giriĢ- Seri çıkıĢlı kaydedici (Parallel in- Serial out-PISO)

IV. Paralel giriĢ- Paralel çıkıĢlı kaydedici (Parallel in- Parallel out-PIPO) olarak sınıflandırılırlar.

I.Seri GiriĢ Seri ÇıkıĢ Kaydediciler

Seri giriĢ seri çıkıĢ kaydediciler, bilgiyi tek bir giriĢten kaydedip tek bir çıkıĢtan okuduğumuz

devrelerdir. Bu kaydedicilere bilgi kaydırılarak kaydedilir ve aynı Ģekilde kaydırılarak okunur.

Kaydetme iĢlemine öncelikle en küçük basamaktan baĢlanır. Bir sonraki basamak kaydedildiği anda

bir önceki bilgi sağa kaydırılır.

Örneğin 1010 bilgisinin kaydedilmesi blok diyagram olarak gösterilmiĢtir. Kaydetme iĢlemine

öncelikle en küçük basamaktan baĢlanır. Bir sonraki basamak kaydedildiği anda bir önceki bilgi sağa

kaydırılır. Dört bitlik bilgi 4 saat sinyali ile kayıt edilir. Kayıt edilen bilginin okunması iĢlemi de aynı

Ģekilde kaydırılarak ve dört saat sinyali ile gerçekleĢir.

II. Seri GiriĢ-Paralel ÇıkıĢ Kaydediciler

Kaydıran kaydedicilerin ikinci tipi olan seri giriĢ-paralel çıkıĢ kaydedicide giriĢler aynı Ģekilde seri

olarak tek tek yapılır. Ancak seri giriĢ-seri çıkıĢ kaydedicide farklı olarak giriĢ oluĢtuğun da çıkıĢlar

aynı anda elde edilir. Ayrıca bu kaydedicide diğerinden farklı olarak CLR giriĢi de vardır ve tüm flip

floplara paralel bağlıdır.

Seri giriĢ-Seri çıkıĢ kaydediciden tek farkı tüm çıkıĢlardan dıĢarıya bilgi çıkıĢı olmasıdır. Bu sayede

bilgi okunması daha hızlı olacaktır. Seri olarak yüklenen bilgi flip-flop çıkıĢlarından paralel olarak

göründüğünden bilginin okunması için tetikleme sinyaline ihtiyaç yoktur.

III. Paralel GiriĢ-Seri ÇıkıĢ Kaydediciler

Kaydıran kaydedicilerin üçüncü tipi olan; paralel giriĢ-seri çıkıĢ kaydedicide giriĢler bir defada tüm

flip flopların giriĢine uygulanır ve saat darbesinden sonra kaydedilir. ÇıkıĢ ise en son flip flop

çıkıĢından alınır. Bilginin çıkıĢtan görülebilmesi her bir bit için bir tetikleme sinyalinin uygulanması ile

sağlanır.

IV. Paralel GiriĢ-Paralel ÇıkıĢ Kaydediciler

Paralel giriĢi-paralel çıkıĢ kaydedicide giriĢler bir defada tüm flip flopların giriĢine uygulanır ve bir Clk

sinyali ile beraber kaydedilir. Aynı anda paralel olan çıkıĢta da görülür.

SAYISAL-ANALOG (DAC)

ANALOG-SAYISAL(ADC)

Gerilim, akım, direnç, frekans, yol, hız, zaman, kuvvet gibi büyüklükler Analog büyüklüklerdir. Bu

büyüklükler ilk aĢamada bir transduser ( algılayıcı, sensör) yardımı ile elektriksel büyüklüğe

çevrilirler. Daha sonra analog elektronik kontrol düzenleri ile değerlendirerek analog göstergeler

(ibreli göstergeler) ile ölçülmüĢ olurlar. Günümüzde analog göstergeler, fazla yer kaplamaları,

maliyetlerinin fazla oluĢu, okuma hatalarına ve güçlüklerine sebep olmaları sebebiyle yerlerini yavaĢ

yavaĢ dijital (sayısal) göstergelere bırakmaktadır. GeçmiĢte tamamen analog göstergelerle

donatılmıĢ bir makine kontrol panosu, günümüzde dijital göstergelerle donatılarak hem maliyeti

azaltılmıĢ, hem de hacmi küçültülmüĢtür. Okuma kolaylığı getirmesi de ayrı bir üstünlüktür.

Yine bir makine kontrol düzeninde bulunan birçok analog büyüklüğün bir bilgisayar tarafından

denetlenmesi, verim ve güvenilirlik açısından çok daha yararlı olacaktır. Dijital göstergeler ve

bilgisayarlar için sayısal bilgilere ihtiyaç vardır.

Dijital / Analog Çeviriciler

“1” ve “0” gibi sayısal giriĢ bilgilerinin, akım veya gerilim olarak çıkıĢtan elde edilmesine dijitalden

analoga çevirme ve bu çevirme iĢlemini yapan devrelere de dijital analog çeviriciler denir.

CLK

A

B

C

DAC’nin giriĢine uygulanan dijital bilgi

DAC’nin analog çıkıĢları

Analog / Dijital Çeviriciler

Basınç, sıcaklık gibi fiziksel değiĢimi veya akım, gerilim gibi analog elektrik sinyalini, 1 ve 0 gibi dijital

bilgilere dönüĢtürme iĢlemine analogdan dijitale çevirme iĢlemini yapan devrelere de analog dijital

çeviriciler denir.

Prensip olarak A/D çevirici, giriĢindeki analog bilgiyi çıkıĢında ikilik bilgiye dönüĢtürür. Bir analog

iĢaret dijital iĢarete çevrilirken belirli aralıklarla örnekleme yapılır. Her bir gerilim aralığı için dijital bir

değer karĢılığı vardır. Her nokta için ayrı bir değer karĢılığı olmaz. Bu nedenle oluĢacak hataları

önlemek oldukça zordur.

A/D çeviricilerin en önemli özellikleri: Çözünürlük, doğruluk ve çevrim süresidir.

Çözünürlük: Çevrici çıkıĢının giriĢ değerine verdiği tepkiye çözünürlük denir.

Doğruluk: GiriĢe göre çıkıĢtan elde edilmesi beklenen teorik çıkıĢla, elde edilen çıkıĢın

karĢılaĢtırılmasına doğruluk denir. Gerçek analog değer ile bu sinyale karĢılık gelen dijital ifadesi

arasındaki hatayı gösterir. En küçük değerlikli bit‟in yarısına kadar olan + hatalar kabul edilebilir.

Çevrim Süresi: GiriĢe göre çıkıĢın beklenen durumu alma süresidir.

OPAMPLI kaĢılaĢtırıcı devreler A/D çevirici olarak kullanılır.