DENEY-6

LOJİK KAPILAR VE İKİLİ DEVRELER

Deneyin Amacı: Lojik ikili devrelerde tek ve çift kararlılık durumlarının incelenmesi.

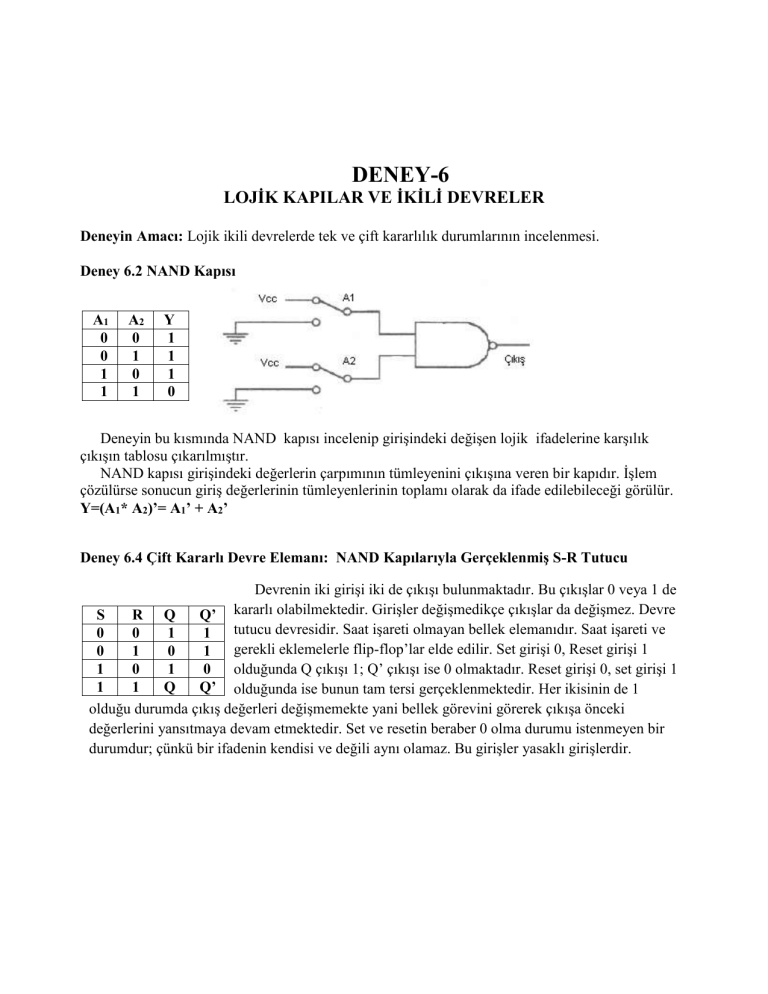

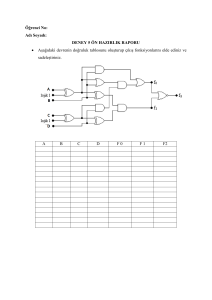

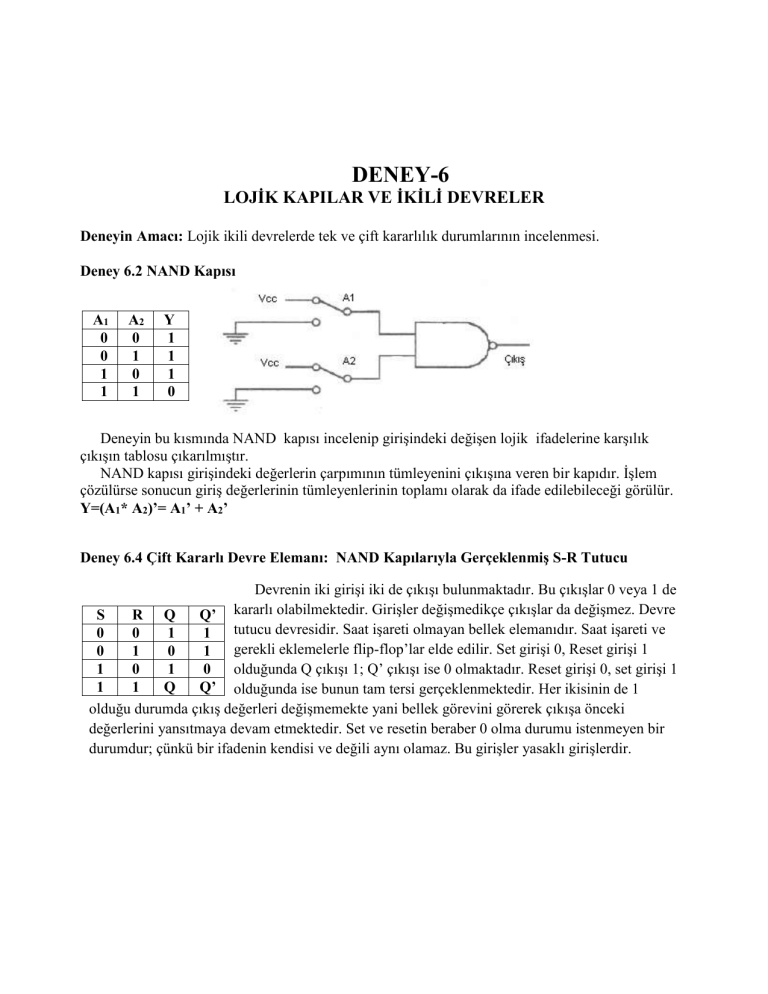

Deney 6.2 NAND Kapısı

A1

0

0

1

1

A2

0

1

0

1

Y

1

1

1

0

Deneyin bu kısmında NAND kapısı incelenip girişindeki değişen lojik ifadelerine karşılık

çıkışın tablosu çıkarılmıştır.

NAND kapısı girişindeki değerlerin çarpımının tümleyenini çıkışına veren bir kapıdır. İşlem

çözülürse sonucun giriş değerlerinin tümleyenlerinin toplamı olarak da ifade edilebileceği görülür.

Y=(A1* A2)’= A1’ + A2’

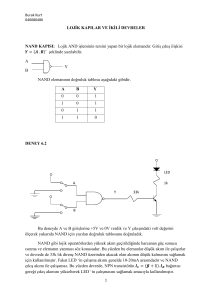

Deney 6.4 Çift Kararlı Devre Elemanı: NAND Kapılarıyla Gerçeklenmiş S-R Tutucu

Devrenin iki girişi iki de çıkışı bulunmaktadır. Bu çıkışlar 0 veya 1 de

S

R Q

Q’ kararlı olabilmektedir. Girişler değişmedikçe çıkışlar da değişmez. Devre

tutucu devresidir. Saat işareti olmayan bellek elemanıdır. Saat işareti ve

0

0

1

1

gerekli eklemelerle flip-flop’lar elde edilir. Set girişi 0, Reset girişi 1

0

1

0

1

1

0

1

0

olduğunda Q çıkışı 1; Q’ çıkışı ise 0 olmaktadır. Reset girişi 0, set girişi 1

1

1

Q

Q’ olduğunda ise bunun tam tersi gerçeklenmektedir. Her ikisinin de 1

olduğu durumda çıkış değerleri değişmemekte yani bellek görevini görerek çıkışa önceki

değerlerini yansıtmaya devam etmektedir. Set ve resetin beraber 0 olma durumu istenmeyen bir

durumdur; çünkü bir ifadenin kendisi ve değili aynı olamaz. Bu girişler yasaklı girişlerdir.

S

Q’

Q

R

SR tutucusu

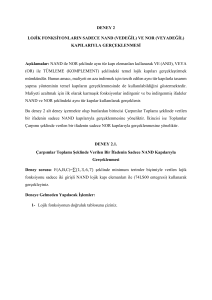

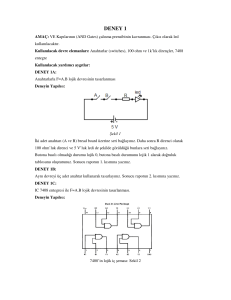

Deney 6.6 Tek kararlı ikili devreler:

Dışarıdan bir uyarı gelmedikçe bir kararlı durumda bulunan devrelerdir. Girişe uygulanacak bir

darbe çıkışın çok kısa bir süre kararlı konumunu değiştirmesine sebep olur. Bu etki geçtikten

sonra devre tekrar kararlı konumuna döner.

Şekil 6.16: Kurulan ve incelenen tek kararlı devre

Vout

II

Vin

III

IV

I

Devre kurulduktan sonra Vin girişine 1Khz’lik işaret verildi.Kare dalganın işlevi tranzistörü ard

arda kesime ve iletime sokarak I girişinde de bir kare dalda elde edilmesidir; fakat bu kare dalga

giriştekinden biraz farklıdır. Tranzistörün işlevinden dolayı lojik 1’de kalma süresi lojik 0’da

kalma süresinden fazladır. Devre ilk çalıştırıldığında ilk Vout çıkışının 1 olduğu görüldü. Bunun

sebebi kondansatörün başlangıçta yüksüz dolayısıyla III noktasındaki ilk gerilimin lojik sıfır

olmasıdır. Bu çıkış 1. NAND kapısına iletilir ve I girişinden 0 geldiğinde bu kapının çıkışı olan

II noktası lojik 1 seviyesine yükselir. Bu durumda kondansatör III noktasının gerilimi de lojik 1

yani 5V değerine çekilmeye çalışılır. (Kapasite dolmaya çalışır fakat kapasitenin dolma

fonksiyonu zamana bağlı olduğu için yeterli zaman olmadığından dolma gerçekleşemez.)

Böylece Vout çıkışı bu işaretin evriği yani lojik 0’dır. Bu işaret birinci NAND kapısının girişine

uygulandığı andan itibaren 1. NAND kapısının çıkışı diğer girişten bağımsız olur. Çünkü 2.

NAND kapısından sürekli lojik 1 gelecektir. Ancak III noktasında elde edilen gerilim değeri

zamanla direnç üzerinden boşalma eğilimi gösterecektir. Buna göre III noktasının gerilimi

direncin değerine bağlı olarak düşecek ve devre bir süre sonra (teoride yaklaşık 2,5 V) lojik 1’den

lojik 0 değerine geçiş yapacaktır. Buna göre devrenin çıkışı bir anda lojik 1’e çıkacakve birinci

NAND kapısının girişlerine lojik 1 değerleri uygulanmış olacaktır. Buna göre birinci NAND

kapısı lojik 0 üretir ve bu olay kondansatör aracılığıyla III noktasını etkiler. Kondansatörün

üzerinde hala yaklaşık 2,5 V gerilim olduğundan bir tarafı 0 V iken diğer tarafını -2,5 V değerine

getirecektir; çünkü uçları arasını gerilimin 5V olarak ayarlamaya çalışacaktır. Bu an devrenin III

noktasında ilk kez negatif bir yük görüldüğü andır. Bu andan itibaren direncin bir ucu 0 diğer ucu -2,5

V olduğundan direnç üzerinden öncekine ters yönlü bir akım oluşacak ve III noktasının gerilimi tekrar

lojik 0’a doğru çekilecektir. Bu durum tranzistörden gelen yeni bir kare işaret gelene kadar devam eder.

Sonra yeniden başlar. Deneyde elde ettiğimiz grafikte -2,5V seviyesi değilde -0,6V seviyesinde bir

değer görülmüştür. Bunun sebebi NAND entegre devresinin ESD diyot içermesidir. Bu diyot

gerilimi sınırlandırıcı olarak görev yapar. Maksimum 5,7V minimum -0,6V aralığında gerilim

elde edilmesini sağlayarak kapıların zarar görmesini engeller. Biri düz, diğeri ters iki diyotun

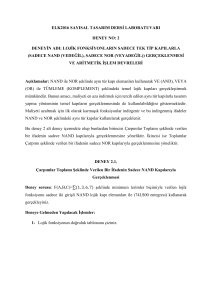

bağlanmasıyla elde edilir. Deneyde elde edilen VR grafiği aşağıdaki gibidir.

VR

5V

2,5V

t

Vc Grafiği:

Deneyden sonucunda Vc’nin kararlı halinin 2.NAND kapısından gelen işarete bağlı olduğu Vc

nin zamanla değişimi grafiğine bakılarak da anlaşılabilir. Önceki deneylerde NAND kapısının

çıkışının lojik 1 olması için girişlerden sadece birinin lojik 0 olması gerektiğini görmüştük.

2. NAND kapısının çıkışından 1.NAND kapısının girişine lojik 0 gelme süresi lojik 1 gelme

süresinden çok fazla olduğu için 1.NAND kapısının çıkışının kararlı durumunun lojik 1 olduğu

görülür. 2. NAND kapısının çıkışından çok kısa süre 1 gelmesi durumunda ise tranzistor ile Vcc

den lojik 1 geldiği sürede Vc sıfıra iner. 0 geldiğinde konumunu değiştirmez. Grafikte de

görüldüğü gibi Vc’nin lojik 0 olduğu durumlar lojik 1 olduğu durumların yanında ihmal

edilebilir. Daha önce belirtildiği tek kararlı devrelerin dışarıdan bir uyarı gelmedikçe konumunu

değiştirmediği görüldü. Dışarıdan gelen etkinin deneyimizde transistor ile Vcc geriliminin

verilmesi olarak belirlendi.

Sonuçlar: İki ve Tek kararlı devrelerin yanı sıra ESD diyotlarının kapılarda kullanılması,

kapasite elemanının çalışma prensibleri ve CMOS kapılarının lojik seviye değişimlerindeki geçiş

karakteristikleri hakkında da detaylı bilgi edinildi.