Haberleşme I DENEY 6 FM DEMODÜLATÖRÜ 6.1 AMA

advertisement

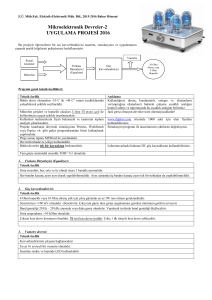

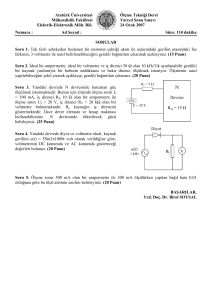

Fatih Üniversitesi Elektrik ve Elektronik Mühendisliği Bölümü EEM 316 – Haberleşme I DENEY 6 FM DEMODÜLATÖRÜ 6.1 AMAÇLAR 1. Faz kilitli çevrimin (PLL) prensibinin çalışılması 2. PLL LM565 ‘in karakteristiğinin anlaşılması 3. FM sinyalinin PLL kullanılarak demodüle edilmesi 6.2 ÖN ÇALIŞMA Kitaptan 5. Üniteyi okuyunuz. 6.3 CİHAZLAR VE MALZEMELER Deney için gerekli malzemeler Tablo 6.1’de listelenmiştir. Deneye başlamadan önce, deneyde kullanılacak olan cihazların model numarasını, seri numarasını ve ofis stok numarasını yazınız. Ayrıca, hasarlı cihazları not ediniz. Tablo 6.1 Deneyde kullanılacak malzeme listesi No: Malzemeler 1 Dijital Osiloskop 2 Sinyal Jeneratörü (1) 3 DC Güç Kaynağı 4 Osiloskop Probları ve Kablolar 5 LM565 PLL Devresi Hasar ve diğer yorumlar: Model Seri No: Ofis Stok No: 6.4 TEMEL BİLGİLER Frekans demodülatörü (frekans diskriminatör) anlık frekans değişikliklerini lineer voltaj değişimine dönüştüren devredir Haberleşme sistemlerinde kullanılan birçok çeşidi vardır. Örneğin; FM’den AM’e dönüştürücü, dengeli, faz farkı diskriminatörleri ve faz kilitli çevrim (PLL) frekans demodülatörü. Bu deneyde PLL frekans demodülatörünün çalışma prensibini öğreneceğiz. EEM 316 – Haberleşme I Deney 6 Sayfa 1/11 6.4.1 Faz Kilitli Çevrimin (PLL) çalışma prensibi PLL, Şekil 6.1’de blok diyagramı gösterilen devre, çıkış ve giriş sinyallerini frekans ve faz türünden kilitleyen geri dönüşümlü elektronik kontrol sistemidir. Radyo haberleşmesinde eğer taşıyıcı sinyalin frekansı iletim esnasında sapmışsa, alıcı devredeki PLL taşıyıcı sinyal frekansını otomatik olarak takip eder. Şekil 6.1 PLL Blok Diyagramı PLL, ilerideki deneylerde iki farklı şekilde kullanılmıştır: (1) demodülatör olarak, faz ve freakans modülasyonunu takip etmek için ve (2) zamanla değişen taşıyıcı sinyalin frekansını takip etmek için. Genellikle, PLL aşağıdaki bölümleri içerir: a) Faz Detektörü (PD) b) Alçak Geçiren Filtre (LPF) c) Gerilim Kontrollü Osilatör (VCO) PLL’in içindeki faz detektörü iki girişine kilitlenir ve iki giriş frekansı eşit ise çıkış olarak sıfır verir. Eğer iki giriş sinyalinin frekansı eşit değilse, detektörün çıkışı AC kısmı kaldıran alçak geçiren filtreden geçerken VCO girişine DC seviye uygulanır. Bu eylem geri besleme döngüsünü kapatır. Çünkü; VCO girişine uygulanan DC seviye, VCO çıkış frekansını giriş frekansıyla tamamen aynı olması için değiştirir. Eğer VCO çıkış frekansı giriş frekansına eşitse, PLL kilitlenmeyi başarmıştır ve kontrol voltajı PLL giriş frekansı sabit olduğu müddetçe sıfır olacaktır. Şekil 6.1’de gösterilen PLL parametreleri aşağıdadır: Kd= faz detektör kazancı volt/radyan Ka= yükseltici kazancı volt/volt Ko= VCO kazancı kHz/volt Kl= Kd Ka Ko = kapalı devre kazancı kHz/radyan Faz detektörünün çalışma prensibinin daha iyi anlaşılması için basit XOR kapısının faz detektörü olarak kullanıldığı düşünülebilir. XOR kapısı, girişleri karşılaştıran ve eşit olmadıklarında darbe sinyali üreten eşitsizlik detektörü olarak düşünülebilir. Çıkış darbesinin genişliği giriş sinyalinin faz hatası ile doğru orantılıdır. Şekil 6.2’de gösterildiği gibi; (b)’nin çıkış darbesinin genişliği, (a)’dan büyük ve (c)’den küçüktür. Alçak geçiren filtrenin girişine faz detektörünün çıkışı uygulandığı zaman, alçak geçiren filtrenin çıkışı darbe genişliği ile doğru orantılı bir DC seviye olması gerekir. Başka bir deyişle, çıkış DC seviyesi giriş sinyallerinin faz hatası ile orantılıdır. Şekil 6.2 giriş faz hatası ile çıkış DC seviyesinin bağıntısını gösterir. EEM 316 – Haberleşme I Deney 6 Sayfa 2/11 Şekil 6.2 Faz algılaması PLL’in çalışma prensibinin daha iyi anlaşılması için başlangıçta PLL’nin kilitli olması durumu düşünülebilir. VCO giriş voltajı 2 V ve serbest hareketli frekansı 1 kHz olsun. Şekil 6.3’teki sinyalleri düşünün. Eğer VCO frekansı ve daha düşük frekanstaki (980 Hz) sinyal A faz detektör XOR’un girişlerine uygulanırsa, daha dar olan çıkış darbesi alçak geçiren filtrenin 1 V’dan daha düşük çıkış voltajı elde etmesine sebep olur. Bu daha küçük voltaj VCO frekansını giriş frekansına yaklaştırarak düşürür. Eğer VCO çıkış frekansı giriş frekansına eşit olursa kilitlenme olur. Tersine, daha yüksek olan 1.2 kHz giriş sinyali B daha büyük olan 3 V filtre çıkışına neden olur. Bu durum sonunda VCO çıkış frekansı giriş sinyaline kilitlenmek için yükselir. Şekil 6.3 Frekans kilitlenmesinin çalışma prensibi EEM 316 – Haberleşme I Deney 6 Sayfa 3/11 6.4.2 LM565 PLL Temel Karakteristikleri LM565 genel amaçlı faz kilitli çevrimdir ve frekans demodülasyonunda yaygın olarak kullanılmaktadır. LM565 ile tasrım yaparken önemli olan parametreler ileride belirtilmiştir 6.4.2.1 Serbest Hareketli Frekans Şekil 6.4 LM565’li bir PLL devresini gösteriyor. Giriş sinyalinin yokluğunda VCO çıkış frekansına serbest hareketli frekans denir. Şekil 6.4’teki PLL devresinde LM565’in serbest hareketli frekansı zaman elemanları C2 ve VR1 ile aşağıdaki formülle bulunur: 1 3.7 VR1C 2 33.6 f o Kapalı devre kazancı: K L = K d K a K o = Vc Serbest hareketli Frekans: f o = (6.1) (6.2) Vc= devreye verilen toplam besleme voltajı= Vcc - ( - Vcc)=5V – (- 5V) = 10V. Şekil 6.4 LM565 PLL devresi 6.4.2.2 Kilitlenme Menzili Başlangıçta VCO herhangi bir frekansta çalışırken PLL zaten kilitlenmiş durumdadır. Eğer giriş frekansı f i VCO frekansı f o ’dan uzaksa hala kilitlenme durumu meydana gelebilir. Giriş frekansı belirli bir frekansa ulaştığında PLL kilitlenmeyi kaybeder. Bu andaki f i ve f o frekans farkına döngünün kilitlenme menzili denir. Kilitlenme menzili aşağıdaki formülle bulunabilir: EEM 316 – Haberleşme I Deney 6 Sayfa 4/11 fL = 8 fO VC (6.3) 6.4.2.3 Yakalama Menzili Başlangıçta çevrim kilitlenmiş ve VCO herhangi bir frekansta çalışıyor olsun. Eğer giriş sinyali f i , VCO frekansı f o ’a yakın olsa bile kilitlenmeme durumu oluşabilir. Giriş frekansı PLL’in kilitlendiği belirli bir frekansa ulaştığı zaman f i ve f o frekans farkına döngünün yakalama menzili denir. LM565’in yakalama menzili aşağıdaki formülle bulunabilir (Şekil 6.5): fc = 1 2π 2π x f L 3.6 x 10 3 x C 2 (6.4) Şekil 6.5 Kilitlenme ve yakalama menzillerinin gösterimi 6.4.3 LM565 PLL’e Dayanan Frekans Demodülatörü Şekil 6.4’teki PLL devresi frekans demodülatörü olarak kullanılabilir. Giriş sinyali frekans cinsinden arttığı zaman, çıkış sinyali voltaj cinsinden düşer. Tersine olarak, eğer giriş sinyali frekans cinsinden düşerse, çıkış sinyali voltaj cinsinden yükselir. LVI565 VCO devresi LM566’ya eşdeğerdir. VCO’nun serbest hareketli frekansı f o , dış parçalar C2 ve VR1 değerleriyle belirlenir. İç direnç 3.6 kΩ (pin7) ve dış kapasitör alçak geçiren filtre oluşturur. Pin 7 ve 8 arasında bağlanan C4 frekans kompansasyon kapasitörüdür. 6.5 DENEY UYGULAMASI VE KAYITLAR Not: DO (dijital osiloskop) kullandığınızda; DO’dan verileri kaydederken, kritik tüm bilgileri kaydedin. Örneğin; DC seviyesi, tepe değeri, periyot ve frekans değerleri. Sonrasında çıkış dalga şeklini düzgün olarak DO çıkışı olarak dereceli grafiğe çiziniz. DO çıkışı sabitlemek için “hold” ve ”storage” özelliklerini kullanınız. EEM 316 – Haberleşme I Deney 6 Sayfa 5/11 6.5.1 LM565 PLL’nin Karakteristik Ölçümleri 1. LM565 PLL devresini yerleştirin. SW2 ’yi C2 = 0.1µF pozisyonuna getiriniz. SW1 ’i OFF pozisyonuna getiriniz. 2. VR1 ’i, VCO OUTPUT’unda maksimum serbest hareketli frekans f oh ve minimum serbest hareketli frekans f ol elde edecek şekilde ayarlayınız. Sonuçları Tablo 6.2’ye kaydediniz. 3. VR1 ’i VCO serbest hareketli frekansı f o = 2 KHz olacak şekilde ayarlayınız. 4. SW1 ’i ON pozisyonuna getiriniz. INPUT (Giriş)’a 0.5Vt-t, 2 KHz’lik kare dalga bağlayınız. 5. INPUT ve VCO OUTPUT sinyallerini gözlemleyiniz ve giriş frekansını çıkış sinyali kilitten çözülene kadar yavaşça arttırınız. Giriş frekansını f Lh olarak Tablo 6.2’ye kaydediniz. 6. Giriş frekansını VCO’nun serbest hareketli frekansı f o ’a geri getiriniz. Giriş frekansını çıkış sinyali kilitten çözülene kadar yavaşça azaltınız ve giriş frekansını f Ll olarak Tablo 6.2’ye kaydediniz. 7. f L = ( f Lh − f Ll ) / 2 eşitliğini kullanarak kilitlenme menzilini hesaplayınız. 8. Giriş frekansını VCO çıkışı kilitten çözülene kadar arttırınız. PLL kilitlenene kadar giriş frekansını yavaşça düşürünüz. Giriş frekansı f Ch ’yi gözlemleyiniz ve sonucu Tablo 6.2’ye kaydediniz. 9. Giriş frekansını VCO çıkışı kilitten çözülene kadar azaltınız. PLL kilitlenene kadar giriş frekansını yavaşça arttırınız. Giriş frekansı f Cl ’yi gözlemleyiniz ve sonucu Tablo 6.2’ye kaydediniz. 10. f C = ( f Ch − f Cl ) / 2 eşitliğini kullanarak yakalama menzilini hesaplayınız. 11. SW1 ‘i OFF pozisyonuna getiriniz. SW2 ’yi C2 = 0.1µF pozisyonuna getiriniz. 2. adımı tekrarlayınız. 12. VR1 ’i VCO serbest hareketli frekansı f o = 20 KHz olacak şekilde ayarlayınız. SW1 ’i ON pozisyonuna getiriniz. INPUT (Giriş)’a 0.5Vt-t, 20 KHz’lik kare dalga bağlayınız. 6’dan 11’e kadar olan adımları tekrarlayınız. EEM 316 – Haberleşme I Deney 6 Sayfa 6/11 6.5.2 LM565 V-F Karakteristik Ölçümleri 1. LM565 PLL devresini yerleştirin. SW2 ’yi C2 = 0.1µF pozisyonuna getiriniz. SW1 ‘i OFF pozisyonuna getiriniz. 2. VR1 ’i VCO OUTPUT’taki serbest hareketli frekans f o = 2 KHz olacak şekilde ayarlayınız. 3. SW1 ’i ON pozisyonuna getiriniz. 4. INPUT (Giriş)’a 0.5Vt-t, 2 KHz’lik kare dalga bağlayınız. PLL OUTPUT ‘u ölçünüz ve Tablo 6.3’e kaydediniz. 5. Giriş frekansını sırasıyla 0.5 kHz, 1 kHz, 1.5 kHz, 2.5 kHz, 3 kHz ve 3.5 kHz olarak değiştiriniz ve çıkış voltajlarını giriş frekanslarıyla ilgili olarak ölçünüz. Sonuçlarınızı Tablo 6.3’e kaydediniz. 6. Çıkış voltajı – giriş frekansı grafiğini Şekil 6.9’a çiziniz. 7. SW2 ’yi C5 = 0.01µ F pozisyonuna getiriniz. 8. SW1 ‘i OFF pozisyonuna getiriniz. VR1 ’i VCO OUTPUT’taki serbest hareketli frekans f o = 20 KHz olacak şekilde ayarlayınız. 9. SW1 ’i ON pozisyonuna getiriniz. 10. INPUT (Giriş)’a 0.5Vt-t, 20 KHz lik kare dalga bağlayınız. PLL OUTPUT ‘u ölçünüz ve Tablo 6.4’e kaydediniz. 11. Giriş frekansını sırasıyla 16.5 kHz, 17.5 kHz, 18.5 kHz, 21.5 kHz, 22.5 kHz ve 23.5 kHz olarak değiştiriniz ve çıkış voltajlarını giriş frekanslarıyla ilgili olarak ölçünüz. Sonuçlarınızı Tablo 6.4’e kaydediniz. 12. Çıkış voltajı – giriş frekansı grafiğini Şekil 6.10’a çiziniz. 6.5.3 PLL Frekans Demodülatörü 1. LM566 FM Modülatör devresini yerleştirin. SW2 ’yi C4 = 0.01µ F pozisyonuna getiriniz. VR1 ’i çıkış serbest hareketli frekansı f o = 20 KHz olacak şekilde ayarlayınız. 2. LM565 PLL devresini SW2 ’yi C5 = 0.01µ F pozisyonuna getirerek tamamlayınız. VR1 ’i VCO OUTPUT’taki serbest hareketli frekans f o = 20 KHz olacak şekilde ayarlayınız. EEM 316 – Haberleşme I Deney 6 Sayfa 7/11 3. LM566 FM Modülatörün çıkışını (OUTPUT) LM565 PLL devresinin girişine bağlayınız ve SW1 ’i ON pozisyonuna getiriniz. 4. LM566 FM Modülatörün AUDIO INPUT’a 300 mVt-t, 1 KHz’lik sinüs dalgası bağlayınız. Osiloskop kullanarak LM565 PLL devresinin çıkış dalga formunu gözlemleyiniz ve Tablo 6.5’e kaydediniz. 5. Adım 4’ü giriş frekansları 2 kHz ve 3 kHz için tekrarlayınız. 6. AUDIO INPUT’un genliğini 500 mVt-t’ye çıkarınız. Adım 4 ve 5’i tekrarlayınız ve sonuçları Tablo 6.6’ya kaydediniz. Tablo 6.2 C fo Serbest Hareketli Frekans Menzili f Oh C2 = 0.1 µF f Ol Kilitlenme Menzili fL f Lh Hz. 2 kHz. Hz. Hz. fL = Hz. C5 = 0.01 µF 20 kHz. Hz. Hz. f Ll Yakalama Menzili fC f Ch f Cl fC = Hz. Hz. Hz. Hz. Hz. fL = Hz. fC = 2.0 2.5 3.0 Hz. Hz. Tablo 6.3 ( Vm = 0.5 V pp , f o = 2 kHz , C2 = 0.1 µF ) Giriş Frekansı (kHz) Çıkış Voltajı (V) EEM 316 – Haberleşme I 0.5 1.0 1.5 Deney 6 3.5 Sayfa 8/11 Çıkış Voltajı (V) 0.5 1.0 1.5 2.0 2.5 3.0 Giriş Frekansı (kHz) 3.5 Şekil 6.9 Çıkış voltajının frekans tarafından değiştirilmesi Tablo 6.4 Vm = 0.5 V pp , f o = 20 kHz , C2 = 0.01 µF Input Frequency (kHz) Output Voltage (V) 16.5 17.5 18.5 20 21.5 22.5 23.5 Çıkış Voltajı (V) 16.5 17.5 18.5 20 21.5 22.5 23.5 Giriş Frekansı (kHz) Şekil 6.10 Çıkış voltajının frekans tarafından değiştirilmesi EEM 316 – Haberleşme I Deney 6 Sayfa 9/11 Tablo 6.5 ( Vm = 300 mV pp , f 0 = 20 kHz ) Giriş Frekansı Giriş Dalga Şekli Çıkış Dalga Şekli 1 kHz 2 kHz 3 kHz EEM 316 – Haberleşme I Deney 6 Sayfa 10/11 Tablo 6.6 ( Vm = 500 mV pp , f 0 = 20 kHz ) Giriş Frekansı Giriş Dalga Şekli Çıkış Dalga Şekli 1 kHz 2 kHz 3 kHz EEM 316 – Haberleşme I Deney 6 Sayfa 11/11