6th International Advanced Technologies Symposium (IATS’11), 16-18 May 2011, Elazığ, Turkey

Euler Yöntemi İle Gerçek Zamanlı Sayısal

İntegrasyon İşleminin FPGA Ortamında

Gerçekleştirilmesi

İ. Soya, T. Tuncer, Y. Tatar

Firat Üniversitesi Elazığ/Türkiye

[email protected], [email protected], [email protected]

Implementation of Real Time Digital Integration

Process with Euler Method on FPGA

Environment

Abstract—In this paper realization of a real-time digital

integration process on FPGA (Field Programmable Gate

Array) platform is explained. To achieve this goal an application

is developed on the floating point number space in FPGA using

Euler integration method also known as the first order

integration method. In this application, the integral value of the

signal created in the FPGA is calculated and it was observed on

the oscilloscope as a continuous time signal.

Keywords—Euler İntegrasyon, FPGA, Floatig Point.

I. GİRİŞ

Ü

RÜN

geliştirme

sürecinde

karmaşık

sistemlerin

davranışını belirlemek için simülasyon çalışmaları önemli

kolaylıklar sağlar. Sistem simülasyonları için sık kullanılan

yazılım araçlarına örnek olarak MATLAB/SIMULINK,

OrCAD, SABER sistem tabanlı veya devre tabanlı yazılımlar

gösterilebilir[1]. Tüm bu simülasyonlar gerçek olmayan

zamanlarda

çalışmaktadır.

Bu

programlar

sistem

performansının çeşitli yönlerini incelemek için yararlı

olmasına rağmen, gerçek zamanda sistemin davranışını

anlamak için yeterli değildir.

Sürekli zamanlı sistemler diferansiyel denklemler ile

modellenir. Diferansiyel denklemlerin çözümü için gerekli

olan integral alma işlemi ise oldukça zaman harcayıcı bir

işlemdir. Diferansiyel denklemleri, gerçek zamanlı olarak

çözebilen analog hesaplayıcılarda operasyonal yükselticiler

(OPAMP) kullanılır. OPAMP’lar integral alıcı, toplayıcı ve

çarpıcı devreler olarak düzenlenip diferansiyel denklem

çözümleri elde edilebilir. Analog hesaplayıcılarda her bir

katsayı değişikliğinde yeni bir eleman değişikliği yapılması

zorunludur.

Diferansiyel denklemlerin gerçek zamanlı olarak, sayısal

ortamda çözümlenmesi için günümüzde FPGA’lı platformların

kullanılması yaygınlaşmıştır. FPGA’lar, mimarilerinin tekrar

programlamaya uygunluğu, tasarımının kolay ve hızlı, işlem

hızının gerçek zamanlı çalışmaya uygun olması gibi

avantajlara sahip olması nedeniyle günümüzde büyük çaplı

projelerin geliştirilmesinde kullanılmaktadır. FPGA’lar,

genellikle sayısal sistemler ve işaretler ile çalıştığı halde, ADC

ve DAC devrelerinin kullanımıyla dış dünyadaki sürekli

zamanlı işaretlerle de gerçek zamanda etkileşebilmektedirler.

FPGA’ların içerisinde uygun donanımsal devrelerin

yaratılması için donanım tanımlama dilleri kullanılır.

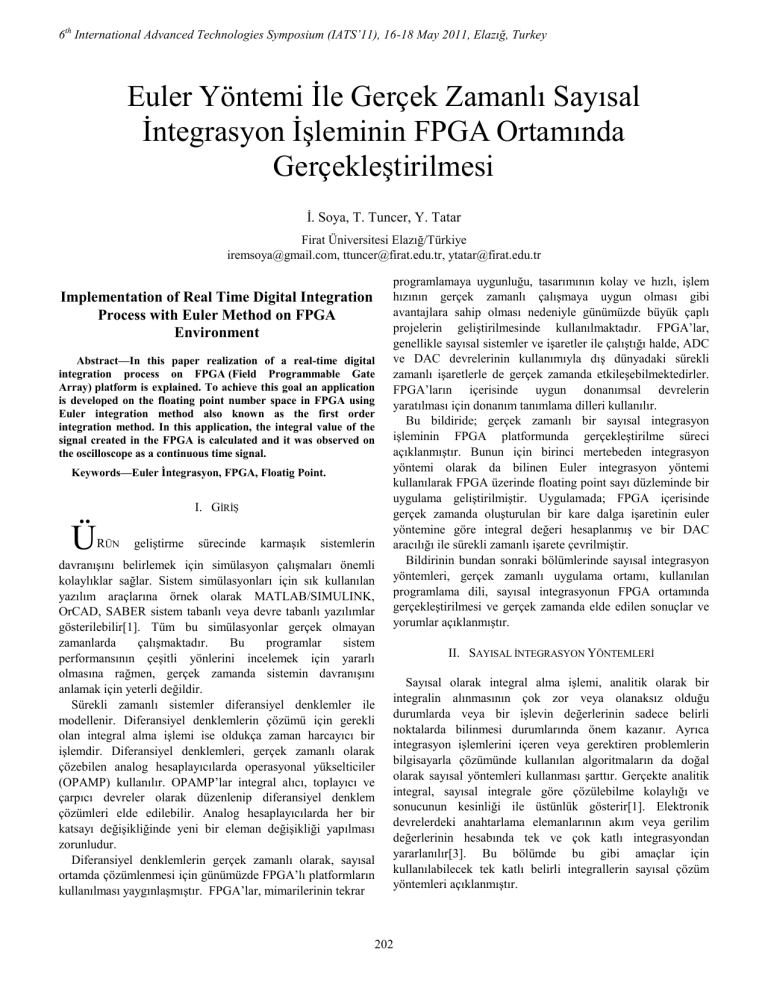

Bu bildiride; gerçek zamanlı bir sayısal integrasyon

işleminin FPGA platformunda gerçekleştirilme süreci

açıklanmıştır. Bunun için birinci mertebeden integrasyon

yöntemi olarak da bilinen Euler integrasyon yöntemi

kullanılarak FPGA üzerinde floating point sayı düzleminde bir

uygulama geliştirilmiştir. Uygulamada; FPGA içerisinde

gerçek zamanda oluşturulan bir kare dalga işaretinin euler

yöntemine göre integral değeri hesaplanmış ve bir DAC

aracılığı ile sürekli zamanlı işarete çevrilmiştir.

Bildirinin bundan sonraki bölümlerinde sayısal integrasyon

yöntemleri, gerçek zamanlı uygulama ortamı, kullanılan

programlama dili, sayısal integrasyonun FPGA ortamında

gerçekleştirilmesi ve gerçek zamanda elde edilen sonuçlar ve

yorumlar açıklanmıştır.

II. SAYISAL İNTEGRASYON YÖNTEMLERİ

Sayısal olarak integral alma işlemi, analitik olarak bir

integralin alınmasının çok zor veya olanaksız olduğu

durumlarda veya bir işlevin değerlerinin sadece belirli

noktalarda bilinmesi durumlarında önem kazanır. Ayrıca

integrasyon işlemlerini içeren veya gerektiren problemlerin

bilgisayarla çözümünde kullanılan algoritmaların da doğal

olarak sayısal yöntemleri kullanması şarttır. Gerçekte analitik

integral, sayısal integrale göre çözülebilme kolaylığı ve

sonucunun kesinliği ile üstünlük gösterir[1]. Elektronik

devrelerdeki anahtarlama elemanlarının akım veya gerilim

değerlerinin hesabında tek ve çok katlı integrasyondan

yararlanılır[3]. Bu bölümde bu gibi amaçlar için

kullanılabilecek tek katlı belirli integrallerin sayısal çözüm

yöntemleri açıklanmıştır.

202

İ. Soya T. Tuncer, Y. Tatar

Genel olarak bir f(x) işlevinin a ≤ x ≤ b aralığındaki belirli

integrali (1)’deki gibi gösterilir.

b

I

f ( x)dx

(1)

a

Bu integrasyon işlemi ile Şekil 1’de gösterildiği gibi

geometrik olarak, integrali hesaplanan f(x) eğrisinin altında

kalan a ≤ x ≤ b aralığındaki taralı alan hesaplanmış olur[2].

Şekil 3: Bir nokta yaklaşımı

b

I

n

f ( x)dx

j 1

a

Şekil 1: İntegral hesabı

Şekil 1’deki taralı alanın, dolayısıyla integralin sayısal

olarak hesaplanması için genellikle a ≤ x ≤ b aralığı, Şekil

2’deki gibi, x uzunluğunda n adet örneğe bölünür. Bu işlem

(2)’deki gibi verilir.

x

ba

n

n

x j f ( x j )

f (x )

j

(3)

j 1

Genellikle örneklemeler eşit x aralıklarında olur. Bu

durumda integral (4) ile hesaplanır. (5)’e göre n örnekleme

sayısı olup, x (b a) n ’dir.

b

I

n

f ( x)dx x

f (x )

(4)

j

j 1

a

B. Yamuk ( Trapez - İki Nokta Yaklaşımı) Yöntemi

Bu yöntemde birbiri ardından gelen her iki nokta bir doğru

ile birleştirilerek Şekil 4’te verilen yamuk şekilli örneklemeler

elde edilir. Böylece integral, alanlarının toplamına eşit olur[2].

(2)

Şekil 2: İntegral hesabında örnekleme

Sayısal olarak integral hesabı yapılırken, her x için f(x)

işaretinin sınırladığı alan hesaplanıp, bir önceki örneklemede

elde edilen alan ile toplanıp integrasyon gerçekleştirilir.

Aslında çarpma ve toplama işlemlerinden oluşan sayısal

integrasyon işleminde önemli olan, n. örnek için f(x)’in

sınırladığı alanın doğru bir şekilde hesap edilmesidir. Bunun

için değişik teknikler geliştirilmiş olup bunlardan bir nokta, iki

nokta, üç nokta ve dört nokta yaklaşımları yaygın olarak

kullanılır[1,2,3]. Gerçek zamanlı sayısal integral alma

işleminde en önemli olgu zamandır. Alan hesaplamasının

mümkün olduğu kadar kısa sürede yapılması istenir.

Dolayısıyla gerçek zamanlı integrasyon işlemlerinde genellikle

bir veya iki noktalı yaklaşımlar kullanılır. Çünkü bu

yaklaşımlarda daha az sayıda matematiksel işlem söz

konusudur.

A. Euler Yöntemi (Bir Nokta Yaklaşımı)

Bir nokta yaklaşımında, Şekil 3’ten görüleceği gibi f(x)

fonksiyonu,

a değerinden başlanarak

x aralıklarla

örneklenir. Bu örnek değerler kullanılarak enleri x, boyları

f(a+ n.x) olan dikdörtgenler elde edilir. Her bir dikdörtgenin

alanı hesap edilip, alanlar toplanarak integralin değeri elde

edilmiş olur.

Şekil 4: İki nokta yaklaşımı

Yamuğun alanı, paralel kenarlarının uzunluklarının

toplamının bu iki kenar arasındaki uzaklığın yarısı ile

çarpımına eşittir. (5)’te oluşan bir yamuğun alanının hesabı,

(6)’da ise f(x) işlevinin yamuk yöntemine göre a ≤ x ≤ b

aralığındaki sayısal integrasyonunun hesabı verilmektedir[2].

xj

f ( x)dx

x j 1

x

( f j 1 f j )

2

b

I

a

f ( x)dx

(5)

x

[ f (a) f (b) 2

2

n 1

f (a jx)]

(6)

j 1

Euler yönteminde, bir alanın bulunması için sadece 1

çarpma ve 1 toplama işlemi yapılacağından, gerçek zamanlı

işlemler için daha uygundur. Fakat integrasyon sonucundaki

hata miktarı fazla olabilir. Yamuk yönteminde ise elde edilen

sonuç daha doğru olmasına rağmen, işlem sayısı daha fazladır.

Her iki yöntemde de örnekleme sayısının fazlalığı sonucun

doğruluğunu etkileyen en önemli faktördür.

Eğer örneklemeler farklı x uzunluklarda ise integralin

hesabı (3) ile yapılır.

203

Euler Yöntemi İle Gerçek Zamanlı Sayısal İntegrasyon İşleminin FPGA…

III. FPGA PLATFORMU VE VHDL DİLİ

Yapılan bu çalışmada FPGA geliştirme platformu

kullanılmasının

sebebi,

yapılan sayısal

integrasyon

programının gerçek zamanlı olarak çalışmasının istenmesidir.

Gerçekleştirilen

integrasyon

işleminin

sonuçlarını

gözlemleyebilmek amacı ile bir DAC kartı kullanılmış ve bu

sayede elde edilen analog çıkışlar osiloskopta izlenmiştir.

FPGA ile DAC entegresi FPGA geliştirme kartı üzerindeki

HSMC konnektör aracılığı ile olmakta ve FPGA kartının

programlanması ise bilgisayar aracılığı ile yapılmaktadır.

Bilgisayar ortamından FPGA geliştirme kartının kontrol

edilebilmesi için Quartus II geliştirme ortamı kullanılmıştır.

Bilgisayar, FPGA geliştirme kartı ve DAC entegresi

kullanılarak oluşturulmuş olan sistemin blok diyagramı Şekil

5’te verilmektedir.

ALTERA Cyclone III Development Board

Bilgisayar

(USB arayüzü)

DAC Entegresi

Şekil 5: Gerçekleştirilen sistemin blok diyagramı

FPGA ile bilgisayar arasındaki iletişim bir RS232 sürücü

devresi ve USB arabirim kartı ile sağlanmaktadır.

Herhangi bir işlevsel modül kendi eşdeğer devre modeli ile

FPGA üzerinde gerçekleştirilebilir. Bu eşdeğer model ardışık

mantık elemanları ve kombinasyonel mantık elemanlarının

kombinasyonudur ve kendinden beklenen işlemi gerçek

zamanda başarabilir. Gerçekleştirilen modülün cevap hızı,

mantıksal elemanların yayılma gecikme toplamının göz önüne

alınmasıyla hesaplanmalıdır[4].

--Kütüphane Tanımlamaları

library ieee ;

use ieee.std_logic_unsigned.all;

--Paket Tanımlamaları

use ieee_proposed.fixed_pkg.all;

--Değişken Tanımlamaları

entity islem is

--tanımlamalar

end islem;

--Program Mimarisi

architecture eulerintegrasyon of islem is

Component sayma is

Port(… );

end component;

begin

--tasarlanan sistemin mimarisi

end eulerintegrasyon;

Yapılan bu çalışmada VHDL donanım tanımlama dili

kullanılmıştır. VHDL dili kullanılarak oluşturulan bir

programın temel yapısı Şekil 6’da verilmektedir.

Quartus II geliştirme ortamında herhangi bir donanım

oluşturabilmek için Verilog veya VHDL ((VHSIC) Very High

Speed Integrated Circuits- Hardware Description Language)

donanım tanımlama dillerinden birinin kullanılması

gerekmektedir.

VHDL donanım tanımlama dilinde gerçekleştirilen bir

sistem Şekil 6’dan da görüldüğü gibi kütüphane tanımlaması,

başlık (entity) kısmı ve mimari (architecture) kısmı olmak

üzere 3 bölümden oluşmaktadır. Programın geliştirilme

aşamasında ilk olarak kullanılacak olan kütüphanelerin

tanımlamaları yapılır. Kullanılacak olan kütüphaneler

programda yer alan değişken tipleri, kullanılan fonksiyon ve

işlemlere göre değişmektedir. Kütüphane tanımlamalarının

ardından paket tanımlamaları yapılır. Paket tanımlamasının

kullanılma nedeni, program içerisinde ayrı bir VHDL

programını

kullanacak

fonksiyonların

bulunmasıdır.

Kütüphane ve paket tanımlamaları tanımlandıktan sonra başlık

kısmı tanımlanır. Bu kısımda program içerisinde kullanılacak

olan giriş-çıkış değişkenleri, bu değişkenlerin tipleri ve

boyutları belirlenir. Başlık kısmı gerçekleştirildikten sonra

mimari bölümüne geçilir. Mimari kısmı kendi içerisinde iki

bölümden oluşmaktadır. İlk bölümü tanımlama ikinci kısmı ise

gerçekleştirme kısmı olarak adlandırılabilir. Tanımlama

kısmında yalnızca gerçeklenen mimari içerisinde geçerli olan

yerel değişkenlerin ve komponentlerin tanımlamaları yapılır.

Komponentler; daha önce yazılmış ve geçerli VHDL kodu ile

aynı dizinde bulunan VHDL kodlarının ve Quartus II

ortamında yer alan işlem bloklarının bu kod içerisinde

çağrılabilmesi için yapılan tanımlamalardır. Mimari kısmının

ikinci bölümünde ise sistemin davranışı tanımlanır. Eğer

sistem ardışıl bir yapıda ise bu kısımda process blokları

oluşturulur.

IV. GERÇEK ZAMAN İNTEGRASYON UYGULAMASI

Sayısal integrasyonlarda yüksek mertebeli teknikler her

zaman en çok tercih edilen yöntemlerdir[2]. Ancak çözüm

tekniği seçilirken programlama maliyetleri ve problemin

doğruluk gereksinimleri gibi faktörler göz önünde

bulundurulmalıdır. Gerçekleştirilen bu çalışmada 48kHz’lik

frekansa sahip bir kare dalga sinyalinin euler yöntemine göre

gerçek zamanlı integrasyon işlemi yapılmıştır. İntegrasyon

işleminde, giriş işareti olarak RAM hafızaya önceden

kaydedilmiş kare dalga işaretinin sayısal değerleri

kullanılmıştır. Gerçek zamanlı integrasyon işlemi kayan nokta

sayı aritmetiğinde yapılmıştır.Gerçekleştirilen sistemde

kullanılan euler yöntemine göre integral alma işlemi (7)’de

verilmektedir.

yi (n) yi (n 1) ei (n 1).t

(7)

Şekil 6: VDHL temel tapısı

Burada, n. örnekleme sürecindeki toplam integral değeri

204

İ. Soya T. Tuncer, Y. Tatar

yi(n), n. örnekteki giriş değeri büyüklüğü ei, örnekleme

periyodu ise t’ ile gösterilmiştir. (7)’deki denklemin FPGA

ortamında çözümü için kullanılan blok şema Şekil 7’de

gösterilmektedir.

en-1

toplamn

Çarpıcı

kaydırmalı olarak çıkışa verilmiştir. Giriş işaretine faz

kaydırması uygulanmasının sebebi; DAC kartına uygulanacak

olan clock sinyali ile sistemi çalıştıran clock sinyalinin

yükselen kenarlarının aynı olmaması dolayısı ile eş zamanlı

olarak çalışmasını sağlamaktır. Pll bloğunun çıkışlarındaki

clock işaretleri Şekil 10’da verilmektedir.

Toplayıcı

c0

toplamn-1

D Flipflop

c1

Şekil 7: Euler yöntemi’nin uygulama blok şeması

Şekil 7’de verilen blok şemasındaki işlemler için akış

şeması Şekil 8’de görülmektedir. Şekil 8’de verilen akış

şemasına göre; RAM’de kayıtlı kayan noktalı sayı sistemindeki

veriler sırası ile okunarak okunan değerler Euler yöntemine

göre örnekleme zamanı ile çarpılmış ardından bir önceki

toplam değeri ile toplanmıştır. Son olarak elde edilen sayısal

veriler DAC kartının girişine gönderilmiştir. Şekil 8’deki akış

şemasını gerçekleştiren donanımsal yapının, Quartus

ortamındaki görünümü Şekil 9’da verilmiştir.

Başla

B. Hazırla Bloğu

Hazırla bloğu FPGA kartının başlangıç koşullarını

sağlayabilmesi için oluşturulmuştur. Bu blok sistemin 50Mzlik

clock işaretini giriş olarak alırken, 3 clock boyunca çıkışa bir

işaret vermez. 3. Clock’tan sonra start biti sürekli lojik 1

seviyesinde tutularak, clock çıkışına da giriş işaretini

vermektedir. Dolayısıyla bu blokta sistemin çalışmaya

başlaması belirlenmektedir.

C. FSM Bloğu

FSM (Finite State Machine – Sonlu Durum Makinesi) bloğu 3

girişli ve 8 çıkışlı bir bloktur. Bu blokta programda

gerçekleştirilen işlemlerin çalışma sıralarını belirlemek için 9

durumlu bir sonlu durum makinesi oluşturulmuştur. Bu blokta

start biti lojik 1 olduğu anda her clock işaretinin yükselen

kenarını sayarak hangi işlemin aktif olması gerektiği

belirlenmektedir. Bu blok içerisinde tanımlanan 8 işlemin çal

lışma süreleri tablo 1’de verilmektedir. İşlemlerin kendileri ise

gerçekleştirildikleri blok içerisinde tanımlanacaktır.

adres = 0

toplam = 0

HAYIR

adres < 32

Şekil 10: Pll bloğunun çıkışları

EVET

Tablo 1: Sonlu durum makinesindeki durumların çalışma süreleri

Durum

İşlem adı

Çalışma

no

süresi(clock)

1

Sayma

1

2

Okuma

1

3

Çarpma

5

4

Toplama

7

5

DFF_32

1

6

Dönüşüm

6

7

DFF_14

1

8

DAC

1

veri = RAM’den veriyi

oku

y = veri .

t

toplamn = toplamn-1+ y

adres = adres +1

DAC girişi = toplamn+1

Şekil 8: Gerçekleştirilen sistemin akış şeması

Şekil 9’daki gibi gerçekleştirilen sistem 4 ana bloktan

oluşmaktadır. Bu bloklar sırası ile pll bloğu, hazirla bloğu,

FSM bloğu ve işlem bloğudur. Sistemdeki hazırla, FSM ve

işlem blokları VHDL dili kullanılarak geliştirilmiştir.

A. Pll Bloğu

Geliştirilen programda kullanılan Altera Pll bloğu tek girişli

ve 2 çıkışlı olarak tanımlanmıştır[5]. Pll bloğunun girişine 50

MHz’lik bir clock işareti uygulanmış ve giriş işareti faz

Tablo 1’de verilen işlem süreleri, program içerisinde

oluşabilecek clock gecikmelerinden etkilenmemek amacı ile

1’er clock fazla sürecek şekilde alınmıştır. Dolayısı ile

programın çalışması esnasında RAM’da bulunan 1 verinin tüm

işlemlerden geçtikten sonra analog veriye çevrilmesine kadar

geçen süre 32 clock olup, 32 clock x 20.83 ns = 665.6 ns’de

tamamlanmaktadır. Bir periyotluk kare dalganın integralinin

alınması için geçen süre ise 1024 clock x 20.83ns = 21.33µs

olmaktadır.

205

Euler Yöntemi İle Gerçek Zamanlı Sayısal İntegrasyon İşleminin FPGA…

Şekil 9: Quartus II ortamında gerçekleştirilen programın blok diyagramı

D. İşlem Bloğu

İntegral alma işleminin gerçekleştirildiği işlem bloğu 8 ayrı

komponent içermektedir. Her bir komponent VHDL dilinde

yazılarak gerçekleştirilmiştir. Bu komponentler, Şekil 6’daki

gibi VHDL dilinde yazılan işlem bloğu içerisinde

kullanılmıştır.

İşlem

bloğu

içerisinde

kullanılan

komponentlerin çalışma sıraları sonlu durum makinesi olarak

gerçekleştirilen FSM bloğu ile belirlenmektedir. Bu blokta

bulunan komponentler sırası ile bu bölümde verilmektedir:

Sayma: Hafıza biriminin hangi adresindeki verinin

okunacağını belirleyen 5 bitlik bir sayıcıdır. Bu komponentin

clock, enable ve reset olmak üzere 3 girişi ve bir de çıkışı

bulunmaktadır. Enable biti lojik 1 olduğu zaman clock

işaretinin yükselen kenarında içeriği bir artarak çıkışa aktarır.

Okuma: Hafıza elemanından Sayma komponenti ile

gösterilen adresteki verinin okunmasını sağlayan blok olup,

enable pini lojik 1 olduğu zaman belirtilen adresteki 32 bit

uzunluğundaki floating point sayıyı çıkışına aktarır.

Çarpma: Bu komponent 2 adet 32 bitlik floating point

sayıyı çarpan blok olup, çarpılan değer hafıza bloğundan

okunan değer iken çarpan hafıza bloğuna kaydedilmiş verilerin

örnekleme zamanı (t) olan 400 ns’dir.

Toplama: Bu komponent 2 adet 32 bitlik floating point

sayıyı toplayan blok olup topladığı değerler; çarpma bloğunun

sonucu ile bir önceki toplamanın sonucudur.

DFF_32: Bu komponent D tipi flip flop’lardan oluşup

toplama komponentinin sonucunu saklamak için kullanılmıştır.

Bu komponentin kullanılmasının sebebi döngünün bir sonraki

değerinde toplama komponentinin bir önceki değerini

almasıdır. Flip flop kullanılmazsa bu değer kaybedilebilir.

Ancak flip flop kullanıldığı için komponentin enable pini lojik

1 olana kadar içerisindeki değer sabit kalmaktadır.

Dönüşüm: Bu komponent 32 bitlik floating point sayının 14

bitlik fixed point sayıya dönüştürmek için kullanılmıştır. Bu

komponentin kullanılmasındaki amaç elde edilen sayısal

verileri analog veriye dönüştürebilmek için kullanılan DAC

kartının 14 bitlik çözünürlüğe sahip olmasıdır. Bu nedenle

floating point formatındaki veriler 14 bit uzunluğundaki

işaretli fixed point verilere çevrilmektedir.

DFF_14: Bu komponent DAC kartının girişine

gönderilecek 14 bitlik fixed point sayı formatındaki sayısal

verilerin saklandığı D tipi bir flip floplardır.

DAC: Son komponent ise enable biti lojik 1 olduğu zaman

parallel iletişim yapan DAC kartının girişlerinin aktif edilerek

sayısal verinin gönderildiği kısımdır.

V. SİMÜLASYON SONUÇLARI

Yapılan bu çalışmada Euler yöntemi kullanılarak gerçek

zamanlı bir sayısal integrasyon işlemi gerçekleştirilmiştir.

Bunun için VHDL dili ile FPGA ortamında ilgili donanımsal

devreler oluşturulmuştur. Sistemin gerçekleştirildiği ortamın

resmi Şekil 11’de verilmiştir. Sistem Quartus II geliştirme

ortamında derlendiğinde; FPGA kartının bu programı

çalıştırırken kullanacağı değişik donanımsal birimler ve

harcanan donanımlar Şekil 12’de verilmektedir.

Sisteme giriş olarak gelen 48 kHz’lik kare dalga

sinyalinden elde edilen sayısal integrasyon sonuçları Signal

Tab II Logic Analyzer ve osiloskop aracılığı ile gözlenmiştir.

Şekil 13’te sistemin Signal Tab II Logic Analyzer ile

gözlemlenen gerçek zamanlı sonuçları görülmektedir.

206

İ. Soya T. Tuncer, Y. Tatar

Şekil 11: Sistemin geliştirildiği ortam

Şekil 12: FPGA kartında kullanılan donanım birimleri

Şekil 13: Signal Tab II Logic Analyzer ile gözlenen sonuçlar

VI. SONUÇLAR

Bu çalışmada, Euler integrasyon yöntemine göre gerçek

zamanlı

integrasyon

işleminin

FPGA

ortamında

gerçekleştirilmesi açıklanmıştır. Tasarım sürecinde VHDL

donanım tanımlama dili kullanılmıştır. İntegrasyon floating

point sayı sistemiyle gerçekleştirilmiştir. Sistemin 1 periyotluk

integrasyon süresi 21.33µs olarak hesaplanmıştır. Bu süre

uzundur. Ancak integrasyon işleminde floating point yerine

fixed point sayı sistemi kullanıldığında bu süre oldukça

kısalabilir. Fixed point sayı sisteminde çalışıldığı zaman

doğruluk oranı nispeten azalacaktır. Fakat gerçek zamanlı

çalışmalarda, aritmetik işlem sürelerini kısalttığı için fixed

point sayı sistemi daha avantajlı olacaktır.

KAYNAKLAR

[1]

[2]

[3]

[4]

[5]

L. T.Pıllace, R.A.Rohrer, C.,Visweswariah, “Electronic Circuit and

System Simulation Medthods”, McGrawhill,pp 75-84,1994.

Ö. Kalenderli, “Sayısal Yöntemler,” http://triton.elk.itu.edu.tr/

~ozcan/DifDenkSayisalCozumu.pdf .

S. C. Chapra, R. P. Canale, “Numerical Methods for Engineers,” 2nd

edition, MC Graw-Hill International Editions, 1990.

K. Jayalakshmi, V. Ramanarayanan,”Real Time Simulation of Electrical

Machines on FPGA Platform,”Proceedings of india international

conference on power electronics,2006.

Altera Corparation, “AN507: Implementing PLL Reconfiguration in

Cyclone III Devices”www.altera.com/literature/an/AN507.pdf.

207