2. TEMEL YAPITAùLARI

advertisement

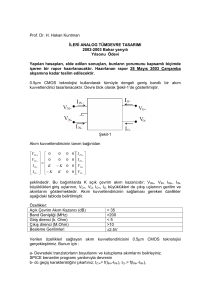

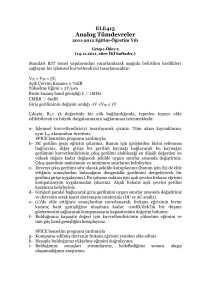

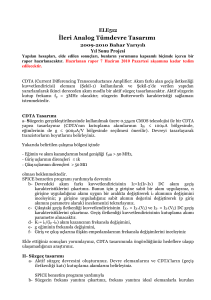

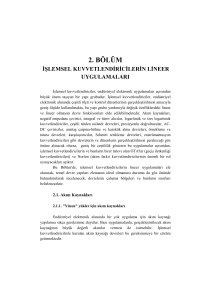

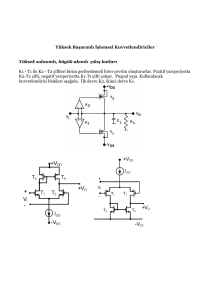

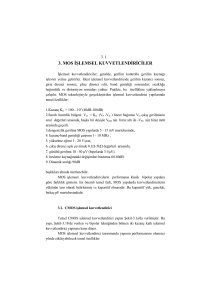

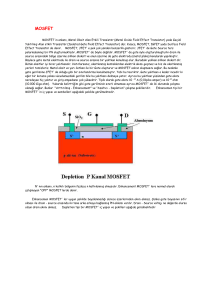

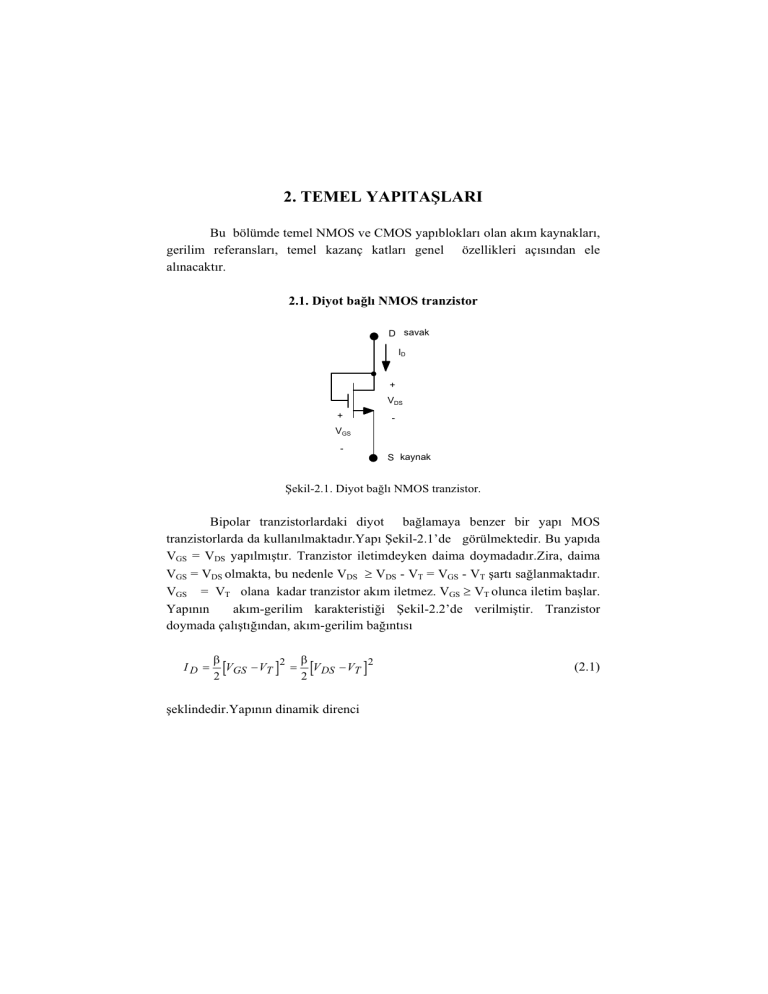

2. TEMEL YAPITAùLARI Bu bölümde temel NMOS ve CMOS yapıblokları olan akım kaynakları, gerilim referansları, temel kazanç katları genel özellikleri açısından ele alınacaktır. 2.1. Diyot ba÷lı NMOS tranzistor D savak ID + VDS + - VGS S kaynak ùekil-2.1. Diyot ba÷lı NMOS tranzistor. Bipolar tranzistorlardaki diyot ba÷lamaya benzer bir yapı MOS tranzistorlarda da kullanılmaktadır.Yapı ùekil-2.1’de görülmektedir. Bu yapıda VGS = VDS yapılmıútır. Tranzistor iletimdeyken daima doymadadır.Zira, daima VGS = VDS olmakta, bu nedenle VDS t VDS - VT = VGS - VT úartı sa÷lanmaktadır. VGS = VT olana kadar tranzistor akım iletmez. VGS t VT olunca iletim baúlar. Yapının akım-gerilim karakteristi÷i ùekil-2.2’de verilmiútir. Tranzistor doymada çalıútı÷ından, akım-gerilim ba÷ıntısı ID E 2 VGS VT @ > 2 E 2 V DS VT @ > 2 úeklindedir.Yapının dinamik direnci (2.1) 2.2 ro 1 gm P . COX 1 W V VT L GS 1 (2.2) E VGS VT ba÷ıntısıyla hesaplanabilir. Görülebilece÷i gibi, dinamik direnç (W/L) ile ters orantılıdır. Yapının geniú bir uygulama alanı bulunmaktadır. Bunlardan biri olan gerilim bölücü ùekil-2.3’de gösterilmiútir. Yapıda, her bir tranzistor bir direnç gibi kullanılmaktadır. Bunun yanısıra, diyot ba÷lı tranzistor, kutuplama elemanı ve aktif yük olarak da uygulama alanı bulmaktadır. ùekil-2.2. Diyot ba÷lı NMOS tranzistorun akım-gerilim karakteristi÷i. +VDD T3 V2 T2 V1 T1 ùekil-2.3. Diyotlu gerilim bölücü. 2.3 2.2. NMOS akım aynaları Basit akım aynası, Wilson akım aynası, kaskod akım aynası gibi bipolar tekni÷inden bilinen yapılar MOS tekni÷ine de uygulanabilmektedir. Basit akım aynası Iref IO T1 + T2 IO Iref T1 + T2 VBE - VGS - (a) (b) ùekil-2.4. NMOS basit akım aynası ve bipolar tekni÷indeki karúılı÷ı. Basit akım aynası devresi ùekil-2.4’de verilmiútir. Devrenin karúı düútü÷ü bipolar tranzistorlu akım kayna÷ı yapısı da yine úekilde gösterilmiútir. Tranzistorların doymada çalıútıkları varsayımı ile akım-gerilim ba÷ıntıları yazılırsa I ref IO P . COX § W · 2 ¨ ¸ >VGS VT @ © L ¹1 P . COX § W · 2 ¨ ¸ >VGS VT @ © L ¹2 2 2 (2.3) (2.4) Tranzistorların aynı prosesle oluúturuldukları ve geometri dıúında eú özellik gösterdikleri göz önüne alınacak olursa, iki koldaki akımların oranı 2.4 W / L 2 W / L 1 IO I ref (2.5) úeklindedir ve tam olarak 1 yapılabilir. Bipolar tranzistorlu düzenlerde bu oran, tranzistorlar eú olsa bile, baz akımları nedeniyle 1 IO I ref 2 1 EF 1 ba÷ıntısıyla tanımlanır. Basit akım aynasının çıkıú direnci RO 1 O. I O (2.6) olur. Wilson akım kayna÷ı Iref IO Iref IO T1 T3 T2 T1 T3 (a) T2 (b) ùekil-2.5. Wilson akım kayna÷ı NMOS tranzistorlarla gerçekleútirilen Wilson akım kayna÷ı devresi, eúde÷er bipolar yapı ile birlikte ùekil-2.5’de görülmektedir. Bu yapıda da akım yansıtma oranı IO I ref W / L 2 W / L 3 (2.7) 2.5 úeklindedir. Tranzistorların tümüyle eú olmaları halinde IO (2.8) I ref olur. Eúde÷er bipolar yapıda ise akımların iliúkisi IO § E 2 2E · F F ¸ I ref . ¨ ¨ ¸ 2 © E F 2E F 2 ¹ úeklindedir; baúka bir deyiúle, yansıtma oranı birden küçüktür. Her iki yapıda da T3 tranzistoru üzerinden sa÷lanan geribesleme, devrenin çıkıú direncini yükseltmektedir. Küçük iúaret eúde÷er devresi kullanılarak RO çıkıú direnci hesaplanırsa RO rO1 g m3 rO 3 (2.9) ba÷ıntısı elde edilir. rO1 büyüklü÷ü T1 tranzistorunun, rO3 de T3 tranzistorunun çıkıú direnci, gm3 büyüklü÷ü ise T3’ ün e÷imi olmaktadır. gm .ro çarpanı 50-100 mertebesindedir. øyileútirilmiú Wilson akım kayna÷ı Iref IO T4 T1 T3 T2 ùekil-2.6. øyileútirilmiú Wilson akım kayna÷ı. MOS Wilson akım kayna÷ı yapılarında MOS tranzistorların eúik gerilimlerinin büyük olması durumunda, T3 tranzistorunun savak-kaynak gerilimi, T2 tranzistorunun savak-kaynak geriliminden 1V yahut daha fazla 2.6 miktarda yüksek olur; bu da elemanların sonlu çıkıú direnci (kanal boyu modülasyonu etkisi) nedeniyle savak akımı dengesizli÷ine yol açar. Bu nedenle, yapıdaki gerilimleri eúitlemek amacıyla ek bir tranzistor, T4 tranzistoru kullanılır. øyileútirilmiú Wilson akım kayna÷ı ùekil-2.6’da verilmiútir. Devreden kolayca izlenebilece÷i gibi, T2 ve T3 tranzistorlarının VDS gerilimleri, T4 tranzistoru yardımıyla eúitlenmektedir. Kaskod akım aynası Yüksek çıkıú dirençli akım kaynaklarına sıkça gereksinme duyulur. Bunun temel nedenlerinden biri, aktif yüklü kuvvetlendiricilerde yüksek de÷erli gerilim kazancı elde edilmesi yönündeki istektir. Bu amaçla, bipolar tekni÷indekine benzer úekilde kaskod akım kayna÷ı gerçekleútirilir. Yapı ùekil2.7’de verilmiútir. Bu yapıda T2 tranzistoru T1 tranzistorunu çıkıú ucundaki gerilim de÷iúimlerinden yalıtmaktadır. ùekil-2.8’de verilen küçük iúaret eúde÷er devresi kullanılarak çıkıú direnci hesaplanırsa RO rO 2 (1 g m2 rO1 ) (2.10) Iref IO T4 T2 T3 T1 ùekil-2.7. Kaskod akım aynası. 2.7 gmb2.vbs2 gm2.vgs2 T2 + ro2 + vx - vgs2 ix ix vx - T1 ro1 ùekil-2.8. Kaskod devrenin çıkıú direncinin hesaplanması elde edilir. Di÷er bir deyiúle, tranzistorun çıkıú direnci 1+gm.rO çarpanı ile çarpılarak çıkıúa yansımaktadır. Gerçekte, çıkıú direncini hesaplarken gövde etkisini de dikkate almak gerekir; zira, T2 tranzistorunun kaynak ucu toprak potansiyelinde de÷ildir. Bunun için ùekil-2.8’deki eúde÷er devreden hareket edilirse RO rO 2 >1 ( g m2 g mb 2 )rO1 @ rO1 (2.11) olur. Bu sonuçta ilginç olan, gövde etkisinin de çıkıú direncini arttıracak yönde etki etmesidir. MOS tekni÷inde istenilen de÷erdeki yüksek empedans, çok sayıda kaskod katın üst üste yerleútirilmesi ile elde edilebilir. Örnek bir yapı ùekil2.9’da görülmektedir. Bu yapılarda her bir kaskod çıkıú direncini 1+gmro kadar yükseltmektedir. Bipolar tekni÷inde ise, baz akımlarının etkisi nedeniyle, bu mümkün de÷ildir. T6 T3 T5 T2 T4 T1 ùekil-2.9. Üç katlı kaskod akım kayna÷ı. 2.8 MOS akım kaynaklarında tranzistor dengesizliklerinin etkisi ID1 + VGS - T1 ID2 T2 ùekil-2.10. MOS akım aynalarında dengesizlik. ømalat toleransları nedeniyle, birbirinin eúi olan iki tranzistoru gerçekleútirmenin mümkün olamayaca÷ı, tranzistorlar arasındaki farklılıklar nedeniyle akım kaynaklarının performansının olumsuz yönde etkilenece÷i açıktır. ùekil-2.10’daki gibi bir ço÷altmalı akım kayna÷ının tranzistorlarının (W/L) oranları ve VT eúik gerilimleri arasında dengesizlik bulundu÷u varsayılsın. Bu durumda, aynı kutuplama gerilimi yardımıyla kutuplanan tranzistorların savak akımları I D1 P. COX § W · 2 ¨ ¸ >VGS VT1 @ © L ¹1 2 (2.12) I D2 P. COX § W · 2 ¨ ¸ >VGS VT 2 @ © L¹2 2 (2.13) olur. ID 'I D W L ' W L I D1 I D 2 2 I D1 I D 2 §W · §W · ¨ ¸ ¨ ¸ © L ¹1 © L ¹ 2 2 §W · §W · ¨ ¸ ¨ ¸ © L ¹1 © L ¹ 2 (2.14) 2.9 VT 'VT VT 1 VT 2 2 VT 1 VT 2 úeklinde ortalama ve fark büyüklükler tanımlansın. Bunların akım-gerilim ba÷ıntılarında yerlerine konması halinde, yüksek dereceden terimler ihmal edilirse, dengesizlikler nedeniyle akımın nominal de÷erinde ortaya çıkacak ba÷ıl hata 'I D ID W L 2 'VT W VGS VT L ' (2.15) olur. Ba÷ıntıdan görülebilece÷i gibi, akım dengesizli÷inin iki bileúeni bulunmaktadır. Bunlardan birincisi geometriye ba÷lıdır ve kutuplamadan ba÷ımsızdır. økinci bileúen ise eúik dengesizli÷inden kaynaklanmaktadır ve kutuplamaya ba÷lıdır, di÷er bir deyiúle VGS-VT azaldıkça artmaktadır. 2.3. Kuvvetlendirici Yapıları Bu bölümde, NMOS ve CMOS aktif yüklü kuvvetlendirici yapıları ele alınacaktır. ølk baúta, sadece kanal oluúturmalı NMOS yapılar incelenecek, daha sonra kanal oluúturmalı ve kanal ayarlamalı tranzistorların birlikte kullanıldıkları yapılara yer verilecek, en sonda ise CMOS yapılara de÷inilecektir. Aktif yüklü savak çıkıúlı kuvvetlendirici yapısı g mb2.vbs2 ro2 g m2.vgs2 1 s2, d1 +VO g1 + Vi g m1.vgs1 ro1 - s1, g2 , b ùekil-2.11. Savak çıkıúlı kuvvetlendirici ve bu yapının eúde÷er devresi. 2.10 Aktif yüklü savak çıkıúlı bir kuvvetlendirici devresi ùekil-2.11’de gösterilmiútir. Yine, yapının eúde÷er devresi úekil üzerinde yer almaktadır. Devrenin gerilim kazancı eúde÷er devre yardımıyla hesaplanabilir. Devre gövde etkisi de dikkate alınarak incelensin. Eúde÷er devreden hareketle 1 dü÷ümü için akım denklemi yazılır ve düzenlenirse v o ( g m2 g m2 1 / ro1 1 / ro 2 ) g m1 . vi elde edilir.1/ro1 ve 1/ro2 terimlerinin gmb ve gm2 iletkenliklerinin yanında ihmal edilebilecekleri düúünülürse KV g m1 g m2 g mb (2.16) ba÷ıntısı bulunur. Daha önce gövde etkisi için verilen tanımlar kullanılırsa g mb Ob . g m oldu÷undan, gerilim kazancı ba÷ıntısı KV g m1 1 g m2 1 Ob (2.17) úeklini alır. Db 1 1 Ob (2.18) biçiminde yeni bir büyüklük tanımlanırsa, ba÷ıntı KV D b g m1 g m2 (2.19) biçiminde yazılabilir. Bu ba÷ıntılardaki Db büyüklü÷ü gövde etkisi katsayısı adını alır ve de÷eri daima 1 den küçüktür; di÷er bir deyiúle Db büyüklü÷ü, kazancı azaltan bir faktör olarak kendini gösterir. Gövde etkisinin ihmal edilmesi, yani Db = 1 olması durumunda, devrenin gerilim kazancı KV (W / L) 1 (W / L) 2 (2.20) olur. Bu ba÷ıntıdan hareketle, MOS tranzistorlu kuvvetlendiricilerde kazancın neden düúük de÷erli oldu÷u izlenebilir. (W/L) oranlarını istenildi÷i kadar büyük tutmak pratikte olanak dıúıdır. Bu oranın büyük tutulmaya çalıúılması halinde 2.11 parazitik kapasiteler sorun olmaya baúlarlar. Bunun yanısıra, kazancı 10 defa arttırmak üzere, (W/L) oranlarının 100 defa de÷iútirilmesi gerekece÷i de açıktır. Bütün bumların yanısıra, gövde etkisi nedeniyle de kazancın biraz daha düúük çıkaca÷ı dikkate alınmak zorundadır. Aktif yüklü kaynak çıkıúlı kuvvetlendirici +VDD d1 gm.vgs g1 T1 gmb.vbs ro1 + +VI Vi +VO s1, d2 +VO T2 ro2 +VB s2, g2 , b ùekil-2.12. Aktif yüklü kaynak çıkıúlı kuvvetlendirici ve bu yapının eúde÷er devresi. Bipolar tekni÷indekine benzer biçimde, NMOS tranzistorlar kullanılarak emetör (kaynak) çıkıúlı kuvvetlendiriciler gerçekleútirmek mümkündür. Bu úekilde gerçekleútirilmiú bir kuvvetlendirici yapısı ve buna iliúkin eúde÷er devre ùekil-2.12’de görülmektedir. Eúde÷er devreden hareket edilirse, kuvvetlendiricinin gerilim kazancı için KV vo vi gm gm 1 1 D b ro1 ro 2 (2.21) ba÷ıntısı elde edilir. Genelde, ro1 ve ro2 yeteri kadar büyük olduklarından, gmb/Db teriminin yanında ihmal edilebilirler. Böylece, devrenin gerilim kazancı KV vo vi Db (2.22) ve çıkıú direnci de ro olur. 1 gm (2.23) 2.12 Diyot ba÷lı kanal oluúturmalı NMOS un yük olarak kullanılması ùekil-2.13. Diyot ba÷lı kanal oluúturmalı NMOS yüklü savak çıkıúlı kuvvetlendirici ve gerilim geçiú e÷risi. Savak çıkıúlı kuvvetlendirici yapısının özel bir hali olan bu yapı, ilk baúta, kanal ayarlamalı yük ve eúlenik elemanın bulunmadı÷ı zamanlarda, MOS dijital devrelerde kullanılmıútır. Yapı ùekil-2.13’de verilmiútir. Giriú geriliminin bir eúik geriliminden daha az olması durumunda T1 kesime gider ve devreden akım akmaz. Giriú geriliminin eúik gerilimini aúması halinde ise her iki tranzistor doymaya girer ve devre kuvvetlendirici olarak çalıúır. Genel savak çıkıúlı kuvvetlendirici yapısında oldu÷u gibi, bu yapıda da gerilim kazancı, gövde etkisinin ihmal edilmesi durumunda KV g m1 g m2 (W / L) 1 (W / L) 2 (2.24) úeklindedir. Pratik eleman geometrileri için bu ba÷ıntı, maksimum gerilim kazancını 10- 20 de÷erleri arasında sınırlar. Bununla beraber, bu tür eviriciler geniú bandlı, düúük kazançlı ve lineerli÷i yüksek devre oluúturmak açısından yarar sa÷larlar. 2.13 Diyot yüklü NMOS kuvvetlendiricinin frekans cevabı gmb2.vo gm2.vo Csb2 Cgs2 ro2 + RS Cgd1 + VO V1 Cgs1 VI gm1.v1 ro1 Cdb1 CL (a) RS V1 Cgd1 + + VI VO Cgs1 gm1.v1 GLeq CLeq (b) ùekil-2.14. Diyot yüklü kuvvetlendiricinin küçük iúaret eúde÷er devresi. Diyot yüklü NMOS kuvvetlendiricinin frekans cevabı eúde÷er devre yardımıyla incelenebilir. Eúde÷er devre ùekil-2.14’de görülmektedir. Eúde÷er devredeki büyüklükler G Leq (1 / ro1 ) (1 / ro 2 ) g m2 g mb 2 (2.25) 2.14 Cdb1 C gs 2 Csb 2 C L C Leq úeklinde tanımlanmıúlardır. hesaplanırsa KV ( s) Bu (2.26) devre yardımıyla GS ( sC gd 1 g m1 ) VO VI > ( sCin GS ). s(C Leq C gd 1 ) G Leq transfer @ fonksiyonu (2.27) elde edilir. Bu ba÷ıntıdaki Cin giriú kapasitesi Cin C gs1 (1 g m1 / G Leq ). C gd 1 (2.28) ba÷ıntısıyla tanımlanmaktadır. Transfer fonksiyonunun sıfır ve kutupları araútırılırsa sz g m1 C gd 1 s p1 sp2 (2.29) GS Cin (2.30) GLeq CLeq Cgd 1 (2.31) Genelde, Cgd1 küçük de÷erlidir. sz >>|sp1| ve CLeq eúde÷er yük kapasitesi küçük oldu÷undan, |sp2|>>|sp1| olur. Bu nedenle, jZ eksenine yakın olan sp1 baskın kutuptur. Frekans e÷risinin 3 dB düútü÷ü açısal frekans Z3dB s p1 GS Cin (2.32) olur. Yüksek de÷erli alçak frekans kazancı elde edilebilmesi için (W/L) oranı küçük olmalıdır. W geniúli÷inin minimum de÷eri prosesin geometrik rezolüsyonu ile sınırlı oldu÷undan, T nin kanal boyunun uzun tutulması gerekir. Bu ise, Cgs2 ve CLeq kapasitelerinin artmasına, dolayısıyla |sp2| nin düúmesine ve frekans e÷risinin bu kutup tarafından yararlı bölgede daha fazla etkilenmesine neden olur. Bu etki, pozitif gerilim dalgalanmasının biraz azalmasına razı olunarak iki yahut daha fazla parçalı yük tranzistoru kullanılarak giderilebilir. Böyle bir devre ùekil-2.15’de gösterilmiútir. Belirli bir gm1 e÷imi için devrenin yükü tek bir yük elemanına göre yarı geçit alanına gereksinme göstermekte, böylece 2.15 etkin yük kapasitesi CLeq azalmaktadır. Buna karúılık, iki diyot seri ba÷lanarak yük oluúturuldu÷undan, alçak frekanslardaki kazanç önceki devreyle aynı olur. +VDD T3 T2 +VO T1 +VI ùekil-2.15. Parçalı yüklü kuvvetlendirici. Kaskod devre +VDD T3 +VO +VB T2 Vd1 +VI T1 ùekil-2.16a. Kaskod yüklü kuvvetlendirici. Aktif yüklü kuvvetlendiricilerde yük tranzistorları kendilerini süren kata önemli bir kapasitif yük oluúturabilirler. Cgs ve Cgd kapasiteleri sorun yaratmaya baúlarlar, özellikle Cgd kapasitesi Miller etkisi nedeniyle sorun çıkarır. Bu problem kaskod devre yardımıyla çözülebilir. Kaskod devre ùekil-2.16a’da verilmiútir. Kaskod yapıda, T1 tranzistorunun savak ucuna ortak geçitli olarak 2.16 çalıúan T2 tranzistoru ba÷lanmıútır. Devrenin gerilim kazancı eúde÷er devre yardımıyla hesaplanabilir. Giriúten ilk tranzistorun savak ucuna kadar olan kazanç vd 1 vi gm1 D gm 2 b 2 (W / L)1 D (W / L) 2 b 2 (2.33) ikinci tranzistorun kaynak ucundan savak ucuna kadar olan kazanç da vo vd 1 D b3 g m2 1 g m3 D b 2 ba÷ıntısıyla verilir. Buradan hareketle toplam kazanç hesaplanırsa vo vi D b 3 g m1 1 g m3 D b 2 (W / L)1 (W / L) 3 (2.34) bulunur. Miller etkisi nedeniyle Cgd1 kapasitesi vd1 /vi ile çarpılarak giriúe yansır. Bu etkiyi minimum düzeyde tutabilmek üzere, (W/L)1 = (W/L)2 seçilerek vd1 /vi = 1 olması sa÷lanır. (W/L)3 oranı küçük tutularak da istenilen kazanç de÷eri sa÷lanır. Kaskod devrenin frekans cevabı RS V1 + VI V2 VO gm2.v2 g m1.v1 Cgs1 g2 -1 C2 gm3 -1 CLeq ùekil-2.16b Kaskod devrenin küçük iúaret eúde÷er devresi. Kaskod devrenin frekans cevabı eúde÷er devre kullanılarak incelenebilir. Kaskod devrenin eúde÷er devresi ùekil-2.16b’de görülmektedir. Eúde÷er devrede görülen büyüklükler 2.17 1 ro1 g2 g m2 C1 C gs1 (1 g m1 / g m2 ). C gd 1 C2 C gd 1 Cdb1 C gs 2 Csb 2 C Leq C gd 2 Cdb 2 Csb 3 C gs 3 C L (2.35) úeklindedir. Miller teoreminin uygulanmasıyla devrenin transfer fonksiyonu KV ( s) GS g m2 ( sC gd 1 g m1 ) ( sC1 GS ).( sC2 g 2 ).( sC Leq g m3 ) (2.36) olur. Bu transfer fonksiyonunun sıfır ve kutupları sz g m1 C gd 1 (2.37) s p1 GS C1 (2.38) s p2 g2 C2 (2.39) sp3 gm 3 CLeq (2.40) úeklindedir. Pratikte karúılaúılan de÷erler ele alınırsa, _sp1 _ << sz , _sp2_ ,_sp3_ ve böylece sp1 baskın kutup olur. Buna göre, kazanç fonksiyonunun 3 dB düúme frekansı f 3dB GS 2S . C1 (2.41) olur. Tipik olarak gm1 = gm2 oldu÷undan, kaskod devrede Cin giriú kapasitesi (2.42) Cin C1 C gs1 2C gd 1 de÷erindedir. Böylece, 3 dB frekansı da f 3dB GS 2S .(C gs1 2. C gd 1 ) (2.43) olur . (2.28) ve (2.30) ba÷ıntılarıyla karúılaútırılırsa, giriú kapasitesinin küçülmesi nedeniyle band geniúli÷inin artaca÷ı kolayca görülebilir. 2.18 Kanal ayarlamalı NMOS yüklü kuvvetlendiriciler NMOS teknolojisinde karúılaúılan en büyük sorun, yeterli derecede yüksek kazançların elde edilememesidir. Bu sorunun çözülmesi için baúvurulan bir yol, kanal ayarlamalı NMOS tranzistorların yük tranzistoru olarak kullanılmasıdır. Modern NMOS prosesinin getirdi÷i kanal ayarlamalı NMOS tranzistorlar bu sorunun çözümünü sa÷lamaktadır. +VDD T2 +VO T1 VI ùekil-2.17. NMOS kanal ayarlamalı yüklü kuvvetlendirici ve gerilim geçiú e÷risi. +VDD I gövde etkisi olmadan DOYMASIZ + V - I gövde etkisiyle DOYMALI VDD V ùekil-2.18.Kanal ayarlamalı yük tranzistorunun I-V e÷risi. Kanal ayarlamalı yüklü kuvvetlendirici devresi ùekil-2.17’de gösterilmiútir. NMOS kanal ayarlamalı yük tranzistorunun I-V e÷risi ùekil2.18’de verilmiútir. Kanal oluúturmalı doymalı yükten farklı olarak, yük tranzistoru, çıkıú ucu VDD besleme gerilimine ulaúana kadar akım akıtmaktadır. Ayrıca, yük direncinin doymada bulundu÷u bölgede oldukça büyük bir gerilim 2.19 kazancı elde edilmektedir. Baúka bir deyiúle, analog kuvvetlendirme açısından bakıldı÷ında, her iki tranzistorun doymada bulundu÷u bölge önem kazanmaktadır. Eúde÷er devre yardımıyla devrenin gerilim kazancı hesaplanırsa 1 gm1 Ob gm2 KV gm1 gmb KV g m1 g mb 1 Ob (2.44) (W / L) 1 (W / L) 2 (2.45) bulunur. Di÷er bir deyiúle, kazanç iki elemanın e÷imleri oranının l/Ob ye bölünmesiyle hesaplanmaktadır. Ob nin 0.1 mertebesinde oldu÷u düúünülecek olursa, bu yapının kanal oluúturmalı yapıya kıyasla daha yüksek kazanç sa÷layaca÷ı açıktır. MOS emetör ba÷lamalı kuvvetlendiriciler ID1 T1 +VI1 ID2 T2 +VI2 ISS -VSS ùekil-2.19. Kaynak ba÷lamalı kuvvetlendirici. Bipolar tranzistorlu yapılarda oldu÷u kadar MOS tekni÷inde de önemli bir yapıtaúı olan emetör yahut kaynak ba÷lamalı kat ùekil-2.19’da gösterilmiútir. Bu devredeki tranzistorlara iliúkin akım-gerilim ba÷ıntıları, tranzistorların çıkıú dirençlerinin ve gövde etkisinin ihmal edilmesi halinde I D1 I D2 P . COX § W · 2 ¨ ¸ >VGS 1 VT @ © L ¹1 P . COX § W · 2 2 ¨ ¸ >VGS 2 VT @ © L ¹2 2 2.20 úeklinde yazılabilir. Öte yandan giriú fark gerilimi de 'VI VI 1 VI 2 VGS 1 VGS 2 olur. Bu ba÷ıntıların biraraya getirilmesiyle, devreye iliúkin çıkıú fark akımı hesaplanırsa 'I D ªW º 1 P . COX « ». 'VI ¬ L¼ 2 2 I SS ( 'V I ) 2 ªW º P . COX « ¬ 2. L »¼ (2.46) bulunur. Bu ba÷ıntı her iki tranzistorun da doymada kaldıkları varsayılarak elde edilmiútir. Fark edilebilece÷i gibi, elde edilen ba÷ıntı 'V I d 2 I SS ªW º P . COX « » ¬ L¼ (2.47) úartı altında geçerli olmaktadır. E÷er 'V I t 2 I SS ªW º P . COX « » ¬ L¼ (2.48) ise, tranzistorlardan birinin iletkenli÷i di÷erine göre çok yüksektir, bu nedenle bütün akım iletkenli÷i yüksek olan tranzistordan geçer; di÷er bir deyiúle, 'ID = ISS olur. Bipolar emetör ba÷lamalı kuvvetlendirici yapısındakine benzer biçimde, kaynak ba÷lamalı çift de, giriú geriliminin belirli bir de÷eri aúması halinde, sınırlayıcı etkisi gösterir. Ancak, bipolar emetör ba÷lamalı kuvvetlendirici yapısından farklı olarak, kaynak ba÷lamalı yapıda bu sınırlama kutuplama akımına ve elemanın boyutlarına ba÷lıdır. Bu açıdan bakıldı÷ında, yapı, bipolar tranzistorlarda emetöre seri direnç ba÷lanarak giriú gerilimi de÷iúim aralı÷ının istenen de÷ere getirilmesine benzer bir davranıú gösterir. Çıkartılan ba÷ıntılardan, bir tranzistorun kesime sürülebilmesi için gerekli olan fark giriú geriliminin, denge konumunda çalıúan tranzistorlara iliúkin VGS-VT de÷erinin (2)0.5 katı olması gerekece÷i bulunabilir. Kutuplama akımını arttırarak, kanal boyunu arttırarak ve kanal geniúli÷ini azaltarak, her iki elemanın da aktif oldukları bölgenin sınırları geniúletilebilir. øúlemsel kuvvetlendirici giriú katlarında VGS-VT birkaç yüz 2.21 milivolt mertebesinde tutulur. Böyle bir yapının farklı kutuplama durumları için elde edilecek geçiú karakteristikleri ùekil-2.20’de görülmektedir. Analog uygulamalar için önem taúıyan di÷er bir büyüklük de kaynak ba÷lamalı katın e÷imidir. Bu e÷im Gm § d'I D · ¨ ¸ © d'V I ¹ 'VI (2.49) 0 úeklinde tanımlanmaktadır. 'ID için verilmiú olan (2.46) ba÷ıntısından türev alınırsa d'I D d'V I ªW º 1 P . COX « ». ¬ L¼ 2 ªW º 1 P . COX « ». ¬ L¼ 2 2 I SS ( 'V I ) 2 ªW º P . COX « ¬ 2. L »¼ 'V 2 I (2.50) 2 I SS ( 'V I ) 2 ªW º P . COX « ¬ 2. L »¼ bulunur. 'VI =0 olması, yani sükunet úartı altında e÷im ba÷ıntısı Gm g m1 g m2 ªW º I SS P . COX « » ¬ L¼ (2.51) úeklini alır. Di÷er bir deyiúle, kaynak ba÷lamalı çiftin e÷imi, bipolar yapılardaki gibi, her bir tranzistorun sükunetteki e÷imine eúittir. Ancak, bipolar yapılarda e÷im sadece kutuplama akımına ba÷lıdır ve eleman boyutlarından ba÷ımsızdır. MOS fark kuvvetlendiricilerinde ise e÷im hem kutuplama akımına hem de elemanın boyutlarına ba÷lı olmaktadır. 2.22 'IO azalan (VGS-VT)'VI=0 'VI ùekil-2.20. MOS fark kuvvetlendiricisinin geçiú karakteristi÷i. +VDD RL2 RL1 + VO - T1 T2 + VOS - ISS - -VSS ùekil-2.21. MOS fark kuvvetlendiricisinde dengesizlik. Kaynak ba÷lamalı çiftin incelenmesi gereken di÷er bir özelli÷i de giriú dengesizlik gerilimidir. øncelemede basitlik sa÷lamak amacıyla devrede yük olarak RL dirençlerinin kullanıldı÷ı varsayılsın (ùekil-2.21). Giriú dengesizlik gerilimine neden olan baúlıca etkenlerin yük dirençlerinin, tranzistorların W/L oranlarının ve eúik gerilimlerinin de÷erleri arasındaki dengesizlikler oldu÷u kabul edilirse, dengesizlik gerilimi VOS VGS 1 VGs 2 VOS VT 1 2. I D1 VT 2 P . COX (W / L) 1 2. I D 2 P . COX (W / L) 2 (2.52) biçiminde ifade edilebilir. Daha önce de yapıldı÷ı gibi, fark ve ortalama büyüklükler tanımlanırsa 2.23 'I D I D1 I D 2 I D1 I D 2 ID 2 §W · §W · §W · '¨ ¸ ¨ ¸ ¨ ¸ © L ¹ © L ¹1 © L ¹ 2 §W · §W · ¨ ¸ ¨ ¸ © L ¹1 © L ¹ 2 §W · ¨ ¸ © L¹ 2 'VT VT 1 VT 2 VT 1 VT 2 VT 2 'RL RL1 RL 2 RL (2.53) RL1 RL 2 2 elde edilir. VOS giriú dengesizlik gerilimi, tanım olarak, eleman toleransları nedeniyle ortaya çıkacak fark çıkıú gerilimini tam olarak sıfır yapan giriú gerilimidir ve ID1.RL1 = ID2.RL2 úartını gerktirmektedir. Bu úart ve yukarıda tanımlanan büyüklükler VOS için elde edilen ba÷ıntıya götürülür ve yüksek dereceden terimler ihmal edilirse, giriú dengesizlik gerilimi VOS 'VT VGS VT 2 ª§ 'R L · § ' (W / L) ·º ¸» ¸¨ «¨ ¬© R L ¹ © (W / L) ¹¼ (2.54) ba÷ıntısıyla verilebilir. Bu ba÷ıntıda 'RL, 'VT, '(W/L) iki eleman arasındaki fark bileúenlerini, RL, VT ve (W/L) de ortalama de÷erleri gösterirler. Ba÷ıntıdan fark edilebilece÷i gibi, yük elemanları arasındaki bir dengesizlik veya W/L oranlarındaki bir dengesizlik gerilimi do÷rudan do÷ruya VGS - VT ile çarpılmaktadır. VGS - VT büyüklü÷ü tipik olarak birkaç yüz milivolt mertebesinde olur. Bipolar emetör ba÷lamalı çiftlerde aynı dengesizlik terimleri kT/q ile, yani çok daha küçük de÷erli bir çarpanla çarpılır. Bu nedenle, MOS kaynak ba÷lamalı çift bipolar emetör ba÷lamalı çifte göre, aynı orandaki geometrik dengesizlikler için daha yüksek bir giriú dengesizli÷i gösterir. 2.24 Doymalı kanal oluúturmalı yüklü fark kuvvetlendiricisi Doymalı kanal oluúturmalı yüklü fark kuvvetlendiricisi ùekil-2.22’de verilmiútir. +VDD T3 T4 +VO1 +VO2 +VI1 T1 +VI2 T2 ISS -VSS ùekil-2.22. Doymalı kanal oluúturmalı yüklü fark kuvvetlendiricisi. Küçük iúaret eúde÷er devresinden yararlanılırsa, devrenin fark gerilim kazancı Kd D b 3 gm1 gm 3 (2.55) ortak iúaret kazancı KC D b1D b 3 (2.56) 2. RS . g m3 ortak iúareti zayıflatma oranı da CMRR Kd KC 2 g m1 .RS (2.57) D b1 olur. Fark iúaret kazancını veren (2.55) ba÷ıntısında gm1 ve gm3 büyüklükleri (W/L) oranları cinsinden yerlerine konursa Kd D b 3 g m1 g m3 D b 3 (W / L) 1 (W / L) 3 (2.58) ba÷ıntısı elde edilir. Daha önce tek katlı doymalı kanal oluúturmalı yüklü kuvvetlendirici için elde edilen sonuçlarla karúılaútırılırsa, bu ba÷ıntının önceki ba÷ıntı ile aynı oldu÷u kolayca fark edilebilir. 2.25 Kanal ayarlamalı yüklü fark kuvvetlendiricisi +VDD T3 +VO1 +VO2 +VI1 1 T1 T2 +VI2 ISS -VSS ùekil-2.23. Kanal ayarlamalı yüklü fark kuvvetlendirici. Fark kuvvetlendiricisi gerçekleútirilirken, yük olarak kanal ayarlamalı tranzistorlardan yararlanmak da mümkündür. Böyle bir yapı ùekil-2.23’de görülmektedir. Devrenin simetrik olması, T1 -T2 ve T3 -T4 ün eú geometriye sahip olmaları úartı altında, Kd fark iúaret kazancı Kd g m1 g mb 1 Ob (W / L) 1 (W / L) 3 (2.59) olur. Tek katlı aktif yüklü kuvvetlendiricilerde oldu÷u gibi, bu yapıda da aktif yük olarak kanal ayarlamalı tranzistor kullanılması, kanal oluúturmalı doymalı yüklü kuvvetlendiriciye göre kazancın 1/Ob kadar daha yükselmesi sonucunu getirmektedir. 2.26 Diferansiyelden tek uca dönüútürücü +VDD +V1 T1 T3 VID +V2 +VO T2 T4 -VSS ùekil-2.24. Diferansiyelden tek uca dönüútürücü. Bir çok durumda fark kuvvetlendiricisinin iki çıkıú ucu arasındaki simetrik gerilimin tek uca dönüútürülmesi istenir. Bunun için kullanılan devre ùekil-2.24’de verilmiútir. Bu devrenin fark iúareti fazla bir kayba u÷ratmadan tek uca çevirmesi gerekir. Yapı, aynı zamanda bir do÷ru gerilim öteleme iúlevini de yerine getirir. Devrenin ne úekilde çalıútı÷ını inceleyelim. T1 tranzistorunun geçidine uygulanan v1 gerilimi bu tranzistorun kayna÷ında aynı fazda elde edildikten sonra T4 tranzistorunun geçidine uygulanır. Baúka bir deyiúle, T1 -T2 çifti kaynak çıkıúlı olarak çalıúır. T3 -T4 çifti ise savak çıkıúlı kat olarak görev yapar ve v1 geriliminin fazını çevirerek bir kez daha kuvvetlendirir. Bundan baúka T3 - T4 çifti kaynak çıkıúlı kat olarak çalıúır ve v2 geriliminin çıkıú dü÷ümüne yansımasını sa÷lar. Böylece, iki ayrı yoldan çıkıú dü÷ümüne ulaúan v1 ve v2 gerilimleri burada aynı yönde toplanarak çıkıú gerilimini oluútururlar. Devrenin gerilim kazancı KV vo g m1 . g m4 | vid g m3 .( g m1 g m2 ) (2.60) úeklindedir. Bu ba÷ıntı çıkartılırken elemanların çıkıú direnci sonsuz büyük olarak alınmıú ve gövde etkisi ihmal edilmiútir. Elemanların tümünün aynı geometriye sahip olmaları halinde kazanç 1/2 olur. Yüksek kazanç elde etmek üzere gm4cün de÷erinin ve bunun için de T4 cün boyutlarını arttırmak gerekir. 2.27 NMOS çıkıú katları NMOS tekni÷inde, eúlenik tranzistor bulunmaması nedeniyle, çıkıú katı tasarımı oldukça sınırlanmıútır. Elemanın çalıúması için gerekli olan büyük de÷erli geçit-kaynak gerilimi çıkıú gerilimi dalgalanmasını sınırlamakta, bunun yanısıra, gm e÷iminin düúük de÷erli olması, düúük empedanslı çıkıú elde edilmesini sınırlamaktadır. NMOS tasarımında en basit çıkıú katı yapısı, daha önce ele alınmıú ve ùekil-2.12’de verilmiú olan kaynak çıkıúlı kuvvetlendiricidir. Bunun iki temel yetmezli÷i bulunur. Birincisi, çıkıú direncinin 1/gm1 olmasıdır. Bu büyüklük sadece büyük sükunet akımlarında ve büyük W/L oranlarında büyüdü÷ünden, düúük de÷erli çıkıú direnci elde edilmesi zordur. +VDD T1 +VI +VO T2 ùekil-2.25. NMOS çıkıú katı. økinci yetmezlik, bipolar emetör çıkıúlı katlarda da oldu÷u gibi, içeriye do÷ru akım akıtma yetene÷inin sınırlı olmasıdır. Bu nedenle, yüksek de÷erli kapasitif yüklerin sürülmesi sırasında sorun çıkabilir. Temel devrenin özel bir biçimi, yük olarak diyot ba÷lamalı tranzistor kullanılmasıdır. Böyle bir yapı ùekil-2.25cde verilmiútir. Daha önce ele alınan yapıda gerekli olan ek kutuplama gerilimi , diyot ba÷lamalı NMOS kullanılarak ortadan kaldırılmıútır. Yine, basit kaynak çıkıúlı devre için yapılan analizlerden elde edilen sonuçlar, diyot ba÷lı NMOS tranzistor için gerekli düzeltmeler yapılmak kaydıyla bu devre için de geçerlidir. gm2 >> go1 , gmb1 úartı altında devrenin gerilim kazancı KV 1 1 g m2 / g m1 (2.61) 2.28 olur. Kazancın bire yakın olabilmesi için 1 >> gm2/gm1 , dolayısıyla gm2 << gm1 olmalıdır; bu ise (W/L)2 << (W/L)1 olmasını, yani bu çıkıú katı için kırmık üzerinde geniú bir alanın harcanmasını zorunlu kılar. +VDD T1 +VI +VO T2 ùekil-2.26. NMOS çıkıú katında kanal ayarlamalı yük kullanılması. Yapının özelliklerinin iyileútirilmesi için baúvurulacak di÷er bir yol, yük olarak kanal ayarlamalı NMOS tranzistor kullanmaktır. Böyle bir yapı ùekil2.26’da görülmektedir. Yapının gerilim kazancı hesaplanırsa KV g m1 g o1 g o 2 g mb1 g m1 1 g o1 g o 2 g mb1 (2.62) bulunur. gm1 >> go1 +go2 + gmb1 úartı altında KV = 1 kabul edilebilir. Söz konusu yapıda, büyük yüzey harcamaya gerek duyulmaksızın bu úart sa÷lanabilir. Devrenin neden olaca÷ı do÷ru gerilim seviye ötelemesi ise (W/L)2 ve (W/L)1 oranları ile ayarlanabilir. Kaynak çıkıúlı katların yukarıda de÷inilen sakıncalarını gidermek üzere de÷iúik düzenler geliútirilmiútir. Negatif geribeslemeli bir çıkıú katı yapısı ùekil-2.27’de verilmiútir. Devrede yer alan tranzistorların savak-kaynak iletkenlikleri sıfır kabul edilirse, gerilim kazancı KV vo vi g m1 / g m2 1 g m4 / g m3 (2.63) 2.29 ùekil-2.27 Negatif geribeslemeli NMOS çıkıú katı. çıkıú direnci de RO 1 g m 3 gm 4 (2.64) olur. (W/L) oranlarının uygun seçilmesiyle KV gerilim kazancı 1’e yaklaútırılabilir. Yine, T3 ve T4 tranzistorlarının W/L oranları büyük tutularak RO çıkıú direnci küçültülebilir. Yüklenme nedeniyle VO çıkıú geriliminde ortaya çıkacak düúme, T2 ve T1 üzerinden T3 tranzistorunun geçidine yansır. T3’ün iletkenli÷i azalır ve çıkıú gerilimi tekrar yükselir. Yapının çıkıú gerilimi pozitif yönde VDD -VGS4 de÷erine kadar, negatif yönde de VSS + VGS3 -VT de÷erine kadar de÷iúebilir. Devrenin akım akıtma yetene÷i de önceki devrelere göre üstünlük göstermektedir. Çıkıú akımı sadece çıkıú tranzistorlarının boyutları ile sınırlıdır. Sistemin geometrisini tayin ederken tatmin edici bir kazanç, maksimum çıkıú salınımı, güç tüketimi ve harcanan kırmık yüzeyi gibi faktörlerin tümünün dikkate alınması gerekir. CMOS kuvvetlendirici yapıları Günümüzde yaygın olarak kullanılan analog MOS tümdevre tekni÷i CMOS (eúlenik MOS) teknolojisidir. Bu teknolojide eúlenik tranzistor bulunmakta, dolayısıyla, bipolar devrelerde oldu÷u gibi, CMOS tekni÷inde de gerilim öteleyici katlara gerek bulunmamaktadır. Hem eúlenik tranzistorun 2.30 bulunmasının sa÷ladı÷ı yararlar, hem de yüksek kazanç sa÷lamaları nedeniyle, CMOS devreler birçok uygulama alanında NMOS devrelere tercih edilmektedir. CMOS evirici S2 +VDD G2 T2 D2 D1 +VI +VO T1 G1 S1 ùekil-2.28. CMOS evirici ve evirici yapısının kesiti. En basit úekliyle bir CMOS evirici ùekil-2.28’de görülmektedir. Bu yapı, dijital devre tekni÷inden bilinen evirici yapısından baúka bir úey de÷ildir. Devreyi oluúturan tranzistorların yapı kesiti de yine úekilde görülmektedir. Bir n kanallı tranzistor ile bir p kanallı tranzistor seri olarak savak uçlarından birbirlerine ba÷lanmıúlardır. VI giriú gerilimi her iki tranzistorun geçit uçlarına birlikte uygulanır. Dijital devrelerdekinden farklı olarak yapı geçiú bölgesinde, her iki tranzistor da doymada olacak úekilde çalıútırılır. Bu bölgede geçiú e÷risinin e÷imi çok yüksektir ve bu nedenle yüksek kazanç de÷erleri elde edilebilir. 2.31 Küçük iúaret hesaplanırsa eúde÷er devresi kullanılarak eviricinin kazancı g o1 1 ro1 (2.65) go2 1 ro 2 (2.66) olmak üzere KV vo vi g m1 g m2 g o1 g o 2 (2.67) bulunur.Bu ba÷ıntıda yer alan ro1 ve ro2 büyüklükleri T1 ve T2 tranzistorlarının kanal boyu modülasyonundan ileri gelen çıkıú dirençleridir. CMOS yapının özelli÷i nedeniyle gövde etkisi etkili olmaz. +VDD T2 RS +VO + VI - T1 CL ùekil-2.29. RS içdirençli bir iúaret kayna÷ı ile sürülen CMOS evirici ve bu eviricinin eúde÷er devresi. CMOS eviricinin ùekil-2.29’daki gibi RS iç dirençli bir VI iúaret üreteciyle sürüldü÷ü varsayılsın. ùekilde verilen eúde÷er devre yardımıyla transfer fonksiyonu hesaplansın. G Leq g o1 g o 2 CLeq Cdb1 Cdb 2 CL 2.32 Cin § g g · m2 Cgs1 Cgs 2 ¨1 m1 ¸. Cgd 1 Cgd 2 G © ¹ Leq olmak üzere KV ( s) VO VI > (2.68) @ GS s(Cgd 1 Cgd 2 ) ( gm1 gm2 ) > ( sCin GS ). s(CLeq Cgd 1 Cgd 2 ) GLeq @ (2.69) elde edilir. Sıfır ve kutuplar hesaplanırsa sz g m1 g m2 C gd 1 C gd 2 s p1 s p2 GS Cin G Leq (2.70) C Leq C gd 1 C gd 2 bulunur. Miller etkisi nedeniyle Cin giriú kapasitesinin de÷eri büyük, bu nedenle de sp1 baskın kutup olur. +VDD T2 T3 +VO Iref +VI T1 ùekil-2.30. Aktif ( akım aynası )yüklü CMOS kuvvetlendirici ve eúde÷er devresi. CMOS tekni÷inde çok sık kullanılan bir yapı da, bipolar tranzistorlu aktif yüklü kuvvetlendirici yapılarına benzeyen p kanallı akım kayna÷ı yüklü devredir. Bu devre ùekil-2.30’da geçiú e÷risi ile birlikte gösterilmiútir. Devre kanal ayarlamalı yüklü eviriciye göre üstünlük gösterir. Hemen hemen negatif besleme geriliminden pozitif besleme gerilimine kadar tüm çıkıú gerilimi dalgalanma bölgesi için her iki tranzistor da doymada olur. Dolayısıyla CMOS evirici NMOS eviriciye göre daha iyi bir çıkıú dalgalanma aralı÷ı gösterir. 2.33 Bunun yanısıra, kutuplama akımlarının ve eleman boyutlarının her iki eleman için uygun olarak seçilmeleri halinde, yapı her iki kayna÷ın birkaç yüz mV yakınına ulaúılana kadar büyük gerilim kazancı sa÷lar. Eúde÷er devre yardımıyla gerilim kazancı hesaplanırsa vo vi KV g m1 g o1 g o 2 (2.71) bulunur. Bu ba÷ıntıda gO1 ve gO2 büyüklükleri n kanallı ve p kanallı tranzistorların çıkıú iletkenlikleridir. Elde edilen ba÷ıntı CMOS eviricinin gerilim kazancının birinci derecede e÷imin eviriciyi oluúturan tranzistorların çıkıú iletkenlikleri toplamına oranıyla belirlendi÷ini göstermektedir. MOS ve bipolar teknolojileri arasındaki temel fark, aktif yüklü kuvvetlendiricinin açık devre gerilim kazancı gm/go nun MOS tranzistorlar için bipolar tranzistorlara göre çok daha düúük olmasıdır. Tipik olarak aynı geometri ve akım de÷erleri için bu oran 10 ila 40 arasındadır. Bu kazanç faktörü, CMOS kuvvetlendirici tasarımında önemli oldu÷undan, açık devre kazancını sınırlayan faktörleri daha ayrıntılı incelemekte yarar vardır. E÷im ve çıkıú dirençleri fiziksel büyüklükler cinsinden yazılırsa §W · 2 P . COX ¨ ¸ I D © L ¹1 g m1 ro1 1 ON . I D ro 2 1 OP . I D (2.72) (2.73) bulunur.Buna göre, gerilim kazancı KV g m1 (ro1 / / ro 2 ) KV 1 ID 1 ON OP §W · 2 P . COX ¨ ¸ © L ¹1 (2.74) olur. Ba÷ıntılardan fark edilebilece÷i gibi 1. E÷im I D , tranzistorların çıkıú dirençleri ise 1/ I D ile orantılıdır; bu nedenle, kazanç 1/ I D ile orantılı olur. 2. Düúük akımda yüksek kazanç elde edilir. 2.34 ùekil-2.31. CMOS kuvvetlendiricide kazancın akıma ba÷ımlılı÷ı. Elde edilen kazanç ba÷ıntısının geçerlilik sınırlarının araútırılması gerekir. (2.74) ba÷ıntısı IDo0 için KVof sonucunu verir. Gerçekte ise böyle de÷ildir. Çıkartılan ba÷ıntı kuvvetli evirtim doyma bölgesi için geçerlidir. Düúük akımlarda çalıúma durumunda zayıf evirtim bölgesine girilir (Bkz: Bölüm-9). Bu bölgede gmaID ve ra1/ID olur; di÷er bir deyiúle e÷im ve çıkıú direncinin savak akımına ba÷ımlılı÷ı bipolar tranzistordaki gibidir, dolayısıyla KV gerilim kazancı akımdan ba÷ımsız olur. Kazancın akıma ba÷ımlılı÷ı ùekil-2.31’de verilmiútir. Verilen bir kutuplama akımı için W/L oranı de÷iútirilerek kazanç arttırılabilir. CMOS fark kuvvetlendirici +VDD T3 + T4 T1 T2 +VO VI go ISS -VSS ùekil-2.32. CMOS aktif yüklü fark kuvvetlendiricisi. 2.35 Eúlenik tranzistorun bulunması, bipolar tranzistorlu aktif yüklü kuvvetlendirici benzeri bir yapıyı mümkün kılar. Yapı ùekil-2.32’de verilmiútir. giriú tranzistorlarının e÷imleri ve çıkıú iletkenlikleri gmi ve gdi, yük tranzistorlarının e÷imleri ve çıkıú iletkenlikleri gml ve gdl ile gösterilirse, devrenin fark, ortak iúaret kazançları ile ortak iúareti zayıflatma oranı, gmi, gml >> gdi ve gdl úartı altında Kd vo vi KC CMRR g mi g di g dl (2.75) g O . g di (2.76) 2. g mi g di g dl 2 g mi .g ml g O .g di (2.77) olarak elde edilir. Puúpul kazanç katları Asimetrik giriú ve çıkıúlı, yüksek kazançlı kat gerçekleútirmenin bir yolu, puúpul kazanç katı gerçekleútirmektir. Bu tür bir devre yapısı, ùekil2.33’de verilmiútir. Bu devrede n kanallı T1 ve p kanallı T2 tranzistorları kaynak izleyici olarak çalıúmaktadır; T3 ve T4 tranzistorları ise ortak geçitli kat iúlevini yerine getirirler. Ortak geçitli katlar, T1 ve T2 üzerinden sürülmektedir. Ortak geçitli katların yükü olarak T5 -T6 ve T7 -T8 akım aynaları kullanılmıútır. Ortak geçitli katlar, rVB simetrik gerilimleriyle kutuplanmıúlardır. Bu kutuplama gerilimlerinin de÷eri VB VTN VTP olacak biçimde seçilmiú ve geçiú distorsiyonu oluúması önlenmiútir. VI = 0 olması durumunda, dört giriú elemanından da küçük bir sükunet akımı akar. VI > 0 ise IX akımı azalırken IY akımı artar. VI < 0 ise IY akımı azalırken IX akımı artar. 2.36 T7 +VDD T8 IX +VB- T1 T4 T2 T3 VO VI IY -V B+ T5 RL IO T6 -VSS ùekil-2.33. Puúpul kazanç katı. Devrenin çıkıú akımı IO I X IY (2.78) oldu÷una göre, giriú geriliminin alaca÷ı de÷erlere ba÷lı olarak çıkıú akımının da pozitif ve negatif de÷erler alaca÷ı açıktır. Kuvvetlendiricideki tranzistorların e÷imleri eú ise, toplam yapının e÷imi Gm g m1 . g m3 g m1 g m3 (2.79) ve gerilim kazancı da KV Gm .( R L / / rO 6 / / rO8 ) (2.80) olur. Puúpul kazanç katı AB sınıfı kuvvetlendirici olarak çalıúır. Büyük genlikli giriú iúareti uygulandı÷ında, çıkıútan akan akım devrenin kutuplama akımından çok yüksek olur. Bu tür bir yapı, özellikle, kapasitif yükleri sürmeye elveriúli olmaktadır. CMOS çıkıú katları CMOS elemanlarla B veya AB sınıfı çıkıú katları gerçekleútirilebilir. Bu tür bir çıkıú katı devresi ùekil-2.34’de geçiú e÷risi ile birlikte verilmiútir. Devre tümüyle bipolar tranzistorlarla gerçekleútirilen devrenin karúılı÷ıdır. T1 -T2 tranzistorları puúpul çalıúan çıkıú katını, T3 -T4 ise bu katı süren sürücü katı oluúturmaktadır. 2.37 VO VTP VTN VA ùekil-2.34. CMOS çıkıú katı ve geçiú e÷risi. Geçiú e÷risinden fark edilebilece÷i gibi, eúik gerilimlerinin büyük olması nedeniyle devrenin geçiú distorsiyonu da oldukça fazladır. Ayrıca gm e÷iminin düúük olması da çıkıú direncinin büyük olmasına neden olur. Yine, bipolar tranzistorlardakine benzer bir yol izleyerek, geçiú distorsiyonunu azaltmak mümkündür. Bu yapı ùekil-2.35’de gösterilmiútir. Burada T5 ve T6 tranzistorları diyot ba÷lamalı olarak devreye iki sürücü tranzistorun geçitleri arasına yerleútirilmiúlerdir ve bipolar tranzistorlu devrelerde kullanılan diyotlara karúı düúerler. +VDD T4 Vkut + VI - T5 T1 T6 T2 +VO RL T3 -VSS ùekil-2.35.AB sınıfı CMOS çıkıú katı. CMOS teknolojisi ile gerçekleútirilen devreler, yapıları gere÷i bipolar tranzistorları da içerirler. ùekil-2.28’deki gibi p kuyulu bir yapıda, n tipi 2.38 +VDD VI T1 IO +Vkut +VDD T4 +VO T1 IO +VO Vkut T2 RL VI -VSS ùekil-2.36Bipolar tranzistorlu çıkıú katı T3 T2 RL -VSS ùekil-2.37. Bipolar tranzistorlu çıkıú katının gerçekleútirilmesi. gövde tranzistorun kolektörü, p tipi kuyu bölgesi tranzistorun bazını, kuyu bölgesi içindeki n tipi savak ve kaynak difüzyonları ise emetörü oluútururlar. CMOS devrelerde hiç bir jonksiyonun iletim yönünde kutuplanmaması için gövde daima en yüksek potansiyelli noktaya ba÷lanır. Bu yüzden bipolar tranzistor sadece emetör çıkıúlı olarak kullanılabilir. Bipolar tranzistorun kullanıldı÷ı bir çıkıú katı yapısı ùekil-2.37’ de verilmiútir. Yapı A sınıfı kuvvetlendirici olarak çalıúır. Bu devrenin sakıncası, çıkıú gerilimi salınımlarının pozitif ve negatif yönde eúit olmaması, iki yöndeki akım akıtabilme kapasitesinin farklı olması, negatif yöndeki salınımın T2 nin kutuplama gerilimi ve akımıyla sınırlanmasıdır. 2.4. Referans gerilimi üreteçleri Elektronikte birçok uygulamada sıcaklıktan olabildi÷ince ba÷ımsız referans gerilimlerine gereksinme duyulur. Referans gerilimi üretmek üzere çeúitli yöntemlerden yararlanılabilir. Bu yöntemlerden VT eúik gerilimi, VGS geçit-kaynak gerilimi farkı referansı MOS tekni÷ine has bir yöntemdir. Bunun yanısıra, CMOS tekni÷inde bipolar tranzistorun bulunmasından da yararlanılarak, bipolar teknolojisinden bilinen kT/q referansı, VBE referansı ve band-aralı÷ı (band-gap) referansı gibi gerilim referanslarının gerçekleútirilmesi de mümkündür. Ayrıca, eúikaltı çalıúmada akım-gerilim ba÷ıntısının üstel olmasından yararlanılarak (Bkz: Bölüm-9) band-aralı÷ı referansı gerçekleútirilmesi gibi MOS teknolojisine has baúka yöntemler de bulunmaktadır. 2.39 Eúik referansı +VDD T3 I T4 T5 I IO T2 T1 R ùekil-2.38. Kendili÷inden kutuplamalı eúik referansı devresi. Kendili÷inden kutuplamalı eúik referansı devresi ùekil-2.38’de görülmektedir. Bu devrede T2 ,T3 ve T4 tranzistorları geribesleme ile T1 tranzistorundan R direncindekine eúit bir akım akmasını sa÷larlar. Böylece devre VGS 1 I . R VT 1 2. I P . COX .(W / L) 1 (2.81) çalıúma noktasında çalıúır. Bu ba÷ıntıda kanal boyu modülasyonu ihmal edilmiútir. Eúitlikteki ikinci terim T1 tranzistoruna iliúkin VGS1 -VT farkını verir ve yeteri kadar büyük (W/L) oranları için yeteri kadar küçüktür. Bu terimin ihmal edilmesi halinde I VT R (2.82) ba÷ıntısı elde edilir. Bu nedenle, devre, eúik gerilimi referansı devresi olarak isimlendirilmektedir. Yapının kötü bir özelli÷i, MOS tranzistorun VT eúik geriliminin de÷erinin tam olarak kontrol edilememesi, tipik olarak 0.5V ile 0.8V arasında bulunmasıdır. Yine, bir MOS tranzistorun eúik geriliminin sıcaklık katsayısı 2.40 -2mV/oC mertebesindedir; difüzyonlu bir direncin sıcaklık katsayısı ise pozitiftir. Bu nedenle, çıkıú akımı büyük de÷erli ve negatif bir sıcaklık katsayısı gösterir; bu da devrenin performansını kötüleútirir. VGS geçit-kaynak gerilimi farkı referansı +VDD R1 R2 _ + Vref - + T1 T2 I -VSS ùekil-2.39. Geçit-kaynak gerilimi farkı referansı. Eúik geriliminden referans gerilimi olarak yararlanmanın di÷er bir yolu, aynı tipten (NMOS veya PMOS) olan, ancak kanal katkı yo÷unlukları, dolayısıyla eúik gerilimleri farklı iki elemandan yararlanmaktır. Bu ilkeye dayanan, dolayısıyla bir kanal oluúturmalı ve bir de kanal ayarlamalı tranzistorun geçit-kaynak gerilimleri arasındaki farktan yararlanılarak gerçekleútirilen referans gerilimi düzeni ùekil-2.39’da görülmektedir. T1 tranzistorunun geçidi ile toprak arasındaki gerilim farkı referans olarak alınırsa Vref VGSE VGSD (2.83) elde edilir. E indisi kanal oluúturmalı, D indisi de kanal ayarlamalı tranzistorları belirtmek için kullanılmıútır. Devrede görülen iúlemsel kuvvetlendirici, negatif geribesleme ile T1 ve T2 tranzistorlarının aynı koúullar altında çalıúmalarını sa÷lar. Referans geriliminin sıcaklı÷a ba÷ımlılı÷ı incelenirse dVref dT d V VGSD dT GSE 2.41 dVref dT d § 1 1 · dI d ¨ ¸ VTE VTD dT k D ¹ dT 2 I © kE (2.84) I § 1 1 dP D 1 1 dP E · ¨ ¸ 2 © k D P D dT k E P E dT ¹ bulunur. Bu ba÷ıntıdaki terimlerin tek tek sıcaklı÷a ba÷ımlılıkları incelenebilir. økinci terimin sıcaklı÷a ba÷ımlılı÷a etkisi kE = kD yapılarak, yani PE .(W/L)E = PD .(W/L)D alınıp sıfıra eúitlenerek ortadan kaldırılabilir. Birinci ve üçüncü terimlere iliúkin de÷iúimlerin ise zıt yönde oldukları fark edilebilir. Bu ise devrenin çıkıú geriliminin sıcaklı÷a ba÷ımlılı÷ının azalaca÷ını göstermektedir. Eúikaltı iletim karakteristi÷i kullanılarak CMOS gerilim referansı elde edilmesi MOS tranzistor çok düúük akımlarda çalıúırken, geçit altındaki kanalda difüzyon akımı baskındır; yani eleman zayıf evirtimde yahut eúikaltı çalıúma bölgesinde çalıúır. Akımın kanal geniúli÷inde mil baúına 10PA’den küçük kalması durumunda, klasik ba÷ıntılar geçersiz olur. Bu bölgede ID savak akımı geçit ve savak gerilimlerine üstel ba÷ımlılık gösterir. +VDD I1 T1 + 'V + V1 - + V2 - I2 T2 ùekil-2.40. Eúikaltı iletim karakteristi÷i yardımıyla gerilim referansı üretilmesi. 2.42 Zayıf evirtimde çalıúan iki MOS tranzistor ùekil-2.40’da gösterildi÷i gibi iki akım kayna÷ı ile kutuplansın. Tranzistorların üzerinde düúen gerilimlerin farkı sıcaklıkla orantılı olur. V1 ve V2 >> kT/q úartı altında, bu fark gerilimi AX n. k ª I 1 .(W / L) 2 º .ln« » q ¬ I 2 .(W / L) 1 ¼ (2.85) olmak üzere 'V V1 V2 AX . T (2.86) bulunur. Burada n prosese ba÷lı bir parametredir. Elde edilen gerilim pozitif sıcaklık katsayılıdır; sıcaklık katsayısı +1500 ppm/oC mertebesinde olur. Bu ilkeye dayanarak oluúturulan band aralı÷ı referansı benzeri bir referans gerilimi üretecinin yapısı ùekil-2.41’de görülmektedir. Devrede 'V geriliminin pozitif + VBE - I2 I1 + V1 - IB T1 + Vref - +VDD + V2 T2 ISS = I1 + I2 -VSS ùekil-2.41. Eúikaltı iletim karakteristi÷ine dayanılarak gerçekleútirilen gerilim referansı devresi. sıcaklık katsayısı, bipolar tranzistorun VBE geriliminin negatif sıcaklık katsayısını kompanze etmektedir. Bipolar tranzistor, CMOS yapıdaki taban npn tranzistoru ile gerçekleútirilmiútir. Devredeki akım kaynakları I1 I SS I 2 !! I 2 2.43 úartı sa÷lanacak, yani akım seviyeleri eúit olmayacak biçimde çalıútırılırlar. Böylece Vref V BE V1 V2 V BE A X . T (2.87) olur. Ba÷ıntıdan fark edilebilece÷i gibi, oluúturulan referans üreteci band aralı÷ı referansına benzemektedir. Yapının çıkıú geriliminin sıcaklık katsayısı, -55oC d T d 100oC aralı÷ında 100ppm/oC de÷erinden küçük tutulabilir. VT = kT/q referansı +VDD T2 T1 Vref I I + _ -VSS ùekil-2.42. Düúey bipolar tranzistorlarla VT referansı gerçekleútirilmesi. CMOS yapıda bulunan düúey (taban) npn tranzistorların kullanılmasıyla gerçekleútirilen bir kT/q referansı ùekil-2.42’de görülmektedir. Bu devredeki akım kaynakları ve iúlemsel kuvvetlendirici CMOS yapılarla gerçekleútirilmiútir. Taban tranzistorlarının emetör kesit alanları A1 (T1 ) ve A2 (T2) ile gösterilsin. Bu kesit alanları arasındaki iliúkinin A1 K . A2 (2.88) olması halinde, devrenin çıkıú gerilimi Vref olur. k.T .ln( K ) q (2.89) 2.44 +VDD T4 T2 T3 T1 + Vref ùekil-2.43. Enine npn tranzistorlarla VT referansı gerçekleútirilmesi. R CMOS yapıda bulunan enine npn tranzistorların kullanılmasıyla gerçekleútirilen bir kT/q referansı ùekil-2.43’de verilmiútir. p kuyulu bir CMOS yapıda, ùekil-2.28’den de fark edilebilece÷i gibi, kaynak (n), kuyu (p) ve savak (n) bölgeleri enine bir bipolar tranzistor oluúturmaktadır. Bunlardan yararlanılarak kurulan kT/q referansı devresinde tranzistorların emetör kesit alanlarının A1 K . A3 ve PMOS tranzistorların (W/L) oranlarının eú olması halinde, devrenin çıkıú gerilimi için Vref k.T .ln( K ) q (2.90) elde edilir. Kendili÷inden kutuplamalı yapı olarak kurulan bu devrede, tüm kendili÷inden kutuplamalı devrelerde oldu÷u gibi, baúlatma problemi vardır ve devreye bir baúlatma devresinin eklenmesi gerekmektedir. ùekilden fark edilebilece÷i gibi üstteki akım aynası nedeniyle tranzistorlardan akacak akımlar eúit olmaya zorlanmaktadır. Bunun yanısıra, bipolar tranzistorların akımları arasında üstel bir ba÷ıntı bulunur. Bu iki karakteristi÷in iki ortak çözümü vardır. Bu çözümler ùekil-2.44’de gösterilmiútir. ùekilden fark edilebilece÷i gibi, Q ile gösterilen çözüm sıfır noktasında ortaya çıkmaktadır ve bu konum istenmeyen bir çalıúma noktasıdır. P ile gösterilen çözüm ise devrenin gerçek çalıúma noktası olmaktadır. Baúlatma devresi ile devrenin daima P noktasında çalıúması sa÷lanır. 2.45 IC3 P IC3 = I C1 Q IC1 ùekil-2.44. Kendili÷inden kutuplamalı VT referansının çalıúma noktası. VT = kT/q referansının zayıf evirtimde elde edilmesi +VDD T4 T2 T3 T1 + R Vref - ùekil-2.45. Zayıf evirtimde çalıúan MOS tranzistorlarla VT referansı. Zayıf evirtimde çalıúan MOS tranzistorların akım-gerilim karakteristiklerinin üstel olmasından yararlanılarak kT/q referansı devresi gerçekleútirmek mümkündür. Bu úekilde çalıúan bir referans gerilimi üreteci ùekil-2.45’de görülmektedir. Devrede yer alan T1 ve T3 NMOS tranzistorları zayıf evirtimde (eúikaltında), T2 ve T4 PMOS tranzistorları ise kuvvetli evirtimde çalıútırılmaktadır. A1 = (W/L)1 , A2 = (W/L)2 , A3 = (W/L)3 ve A4 = (W/L)4 olmak üzere devrenin çıkıú gerilimi hesaplanırsa 2.46 Vref k . T ª A1 A4 º ln . 'VT q «¬ A3 A2 »¼ (2.91) elde edilir. Bu ba÷ıntıdaki 'VT büyüklü÷ü, T1-T3 tranzistorlarının üzerlerinde düúen gerilimler arasındaki dengesizli÷i göstermektedir. Fark edilebilece÷i gibi, Vref gerilimi R direncinden ba÷ımsızdır. Taban pnp tranzistorlar yardımıyla VT üreteci Taban npn tranzistorlarıyla kurulan kT/q referansı üretecinin benzeri, p tabanlı CMOS teknolojisindeki taban pnp tranzistorları yardımıyla da gerçekleútirilebilir. Bu úekilde gerçekleútirilen bir yapı, ùekil-2.46’da verilmiútir. Yapı, kT/q referanslı akım kayna÷ı olarak çalıúır. Yapıda bulunan T1 -T2 taban pnp tranzistorlarının emetör kesit alanları 1:n oranında seçilmiútir. T3, T4 , T5 ve T6 tranzistorları ile kurulan akım kayna÷ı, iki koldan akan akımları eú olmaya +VDD T6 T7 T5 I I I T3 T4 R 1 T1 n T2 ùekil-2.46. Taban pnp tranzistorlarıyla VT üreteci gerçekleútirilmesi. zorlar. Bu durumda tranzistorların baz-emetör gerilimleri arasındaki 'VBE farkı R direncinin üzerindeki gerilime eúit olur. Böylece, elde edilecek akım I k .T .ln( n ) q. R ba÷ıntısıyla hesaplanabilir. (2.92) 2.47 VT ısıl geriliminin sıcaklık katsayısı pozitiftir. Yine, devrede yer alan difüzyonlu direnç de pozitif bir sıcaklık katsayısı gösterir. Devrenin çıkıú akımının sıcaklık katsayısı hesaplanırsa TCVT 1 dVT VT dT TC R 1 dR R dT (2.93) olmak üzere TC I TCVT TC R (2.94) bulunur. Ba÷ıntıdan fark edilebilece÷i gibi, VT refaransı devrelerinde çıkıú büyüklü÷ünün sıcaklık katsayısı, iki pozitif büyüklü÷ün farkı biçimindedir. Bu nedenle, VT referansı devrelerinde sıcaklık katsayısı düúük de÷erli olur. Devrede T3 ve T4 tranzistorlarının VGS gerilimleri arasında oluúacak bir dengesizlik, R direnci üzerindeki gerilim düúümü 100mV’lar mertebesinde oldu÷undan, büyük çıkıú akımı dengesizli÷ine neden olabilir. Yine, tranzistorların VDS gerilimlerinin farklı olması nedeniyle, kanal boyu modülasyonu etkisi ortaya çıkar ve akımlar biririnden farklı olabilir. VGS dengesizliklerini azaltmak üzere, pratikte, büyük tranzistor geometrileri kullanılır. Kanal boyu modülasyonunun etkisinin azaltılması için de kaskod akım kayna÷ı veya Wilson akım kayna÷ı yapılarının kullanılması yoluna gidilir. øyileútirilmiú Wilson akım kayna÷ı kullanılarak gerçekleútirilen bir yapı ùekil2.47’de görülmektedir. T5 +VDD T6 T11 T7 T8 T9 T10 T3 T4 T12 IO R T1 1 T2 n -VSS ùekil-2.47. Wilson akım kaynakları ile devrenin özelliklerinin iyileútirilmesi. 2.48 VBE referansı +VDD T4 T5 T3 I IO I T1 T2 R T6 -VSS ùekil-2.48. Taban pnp tranzistoruyla VBE referansı. p tipi tabandaki parazitik tranzistorlardan yararlanılarak gerçekleútirilen bir VBE referansı devresi ùekil-2.48’de gösterilmiútir. Devredeki T1, T2, T3 ve T4 tranzistorları ile yapıya geribesleme uygulanmaktadır. pnp tipi T1 bipolar tranzistor ile R direncinden akan akımlar, yapının zorlaması nedeniyle, birbirine eúittir. Böylece, devreden hareketle k .T § I . ln¨¨ q © IS I .R VBE · ¸¸ ¹ (2.95) yahut I V BE R (2.96) yazılabilir. Bipolar tranzistorun VBE baz-emetör gerilimi oldukça iyi kontrol edilebilen bir parametredir; bu gerilim %5 hata ile belirlenebilmektedir. Bu tür bir yapının baúlıca sakıncası, VBE geriliminin negatif sıcaklık katsayısı nedeniyle ortaya çıkmaktadır. ùekilde verilen devre için çıkıú akımının sıcaklık katsayısı hesaplanırsa 1 dV BE V BE dT TCVBE (2.97) olmak üzere TC I TCVBE TC R elde edilir. (2.98) 2.49 Yapıda yer alan difüzyonlu direncin sıcaklık katsayısı pozitiftir. (2.98) ba÷ıntısı uyarınca VBE geriliminin negatif sıcaklık katsayısı ile direncin pozitif sıcaklık katsayısı birbirine eklenecek biçimde biraraya gelmektedir. Bu nedenle, çıkıú akımının sıcaklık katsayısının çok yüksek de÷erli ve negatif olaca÷ı açıktır. Band-aralı÷ı referansı CMOS tekni÷inde bulunan bipolar tranzistorlardan yararlanılarak bipolar tekni÷inden bilinen band-aralı÷ı referansının bu teknikle gerçekleútirilmesi mümkündür. Bilindi÷i gibi, VBE geriliminin sıcaklık katsayısı negatif, kT/q ısıl geriliminin sıcaklık katsayısı ise pozitiftir. Bu iki zıt yönlü de÷iúimin VO V BE K .VT (2.99) úeklinde bir gerilim oluúturacak úekilde biraraya getirilmesi halinde, K nın uygun bir de÷erinde ve belirli bir T0 çalıúma sıcaklı÷ında VO geriliminin sıcaklık katsayısı sıfır olur. Bu úartın sa÷landı÷ı gerilim, Si malzemenin yasak enerji bandı gerilime eúit olması nedeniyle, yapı band aralı÷ı gerilimi referansı olarak isimlendirilmektedir. P tabanlı CMOS teknolojisindeki taban pnp tranzistorlarından yararlanılarak gerçekleútirilen bir band aralı÷ı referansı üreteci ùekil-2.49’da verilmiútir. ùekilden fark edilebilece÷i gibi, VBE ve kT/q nun uygun katsayılarla çarpılıp toplanmasıyla band aralı÷ı referansı elde edilmektedir. Devrenin sıcaklık katsayısı, tasarımın yapıldı÷ı T0 sıcaklı÷ında sıfır, bunun dıúındaki sıcaklıklarda da çok düúük de÷erli olur. x büyüklü÷ü, çıkıú geriliminin kT/q ya ba÷lı bileúenini ayarlar. MOS yapılarda iúlemsel kuvvetlendiricinin giriú dengesizli÷i ve giriú dengesizlik geriliminin sıcaklıkla sürüklenmesi yüksek olur ve bu çıkıú gerilimini olumsuz yönde etkiler. 2.50 +VDD T4 T3 T5 T7 T6 T8 IO= T9 VO=VBE+x.VT.ln(n) T10 + R12 T11 _ T1 VO ___ T2 R T12 1 T13 n x.R R12 T14 -VSS n ùekil-2.49. Taban pnp tranzistorlarıyla band aralı÷ı referansı. Düúey (taban) bipolar tranzistorlarıyla gerçekleútirilen band aralı÷ı referansı devresi + + R1 V1 - T6 T2 T4 R2 T1 T3 +VDD + VBE + Vref V2 - - T5 -VSS ùekil-2.50. Taban npn tranzistoruyla band aralı÷ı referansı. 2.51 CMOS yapıda bulunan taban tranzistorlarından yararlanılarak gerçekleútirilen bir band aralı÷ı referansı devresi ùekil-2.50’de verilmiútir. Bu yapıda T2-T4 tranzistorları zayıf evirtimde (eúikaltı bölgesi , bkz. Bölüm-9) çalıútırılmaktadır. Bu nedenle, R1 direncinin üzerindeki gerilim düúümü V1 I D1 . R1 k .T § W / L 2 · .ln¨ ¸ q © W / L 4 ¹ k . T § A2 · .ln¨ ¸ VGS 4 VGS 2 q © A4 ¹ (2.100) olur. R2 direncinin uçlarındaki V2 gerilimi V2 W / L 5 I .R W / L 1 D1 2 I D5 . R2 A5 I .R A1 D1 2 (2.101) úeklinde yazılabilir. Buradan hareket edilir ve devreden yararlanılırsa, Vref gerilimi için Vref V BE V2 V BE A5 R2 k . T § A2 . A3 · R2 .ln¨ ¸ A1 R1 q © A4 . A1 ¹ (2.102) bulunur. Fark edilebilece÷i gibi, devre band aralı÷ı referansı devresi olarak çalıúmaktadır. Enine bipolar tranzistorlarla gerçekleútirilen band aralı÷ı referansı devresi CMOS yapıda yer alan enine bipolar tranzistorlardan yararlanılarak da band aralı÷ı referansı devresi gerçekleútirilebilir. Bu tür bir yapı, ùekil-2.51’de görülmektedir. ùekil-2.51’deki yapıda A<1 alınmıútır; böylece IB1 << IR, dolayısıyla, IR akımının baz akımından etkilenmesi azaltılmıú olur. R1 direncinin uçlarında 'V BE V BE 1 V BE 2 kT .ln( K ) q (2.103) gerilimi oluúur. Devrenin Vref çıkıú gerilimi hesaplanırsa Vref bulunur. VBE 2 kT § R2 · ¨1 ¸.ln( K ) q © R1 ¹ (2.104) 2.52 +VDD T4 T3 + Vref R2 T1 T2 T8 - K.A1 A1 R1 T5 1 T6 T7 A -VSS ùekil-2.51. Enine npn tranzistorlarla band aralı÷ı referansı. KAYNAKLAR [1] [2] [3] [4] [5] [6] [7] [8] [9] H. Kuntman, Analog tümdevre tasarımı, Sistem yayınları, østanbul, 1992. H. Kuntman, Analog MOS tümdevre tasarımı (Endüstri Semineri Notu), øTÜ øleri Elektronik Teknolojileri Araútırma Geliútirme Vakfı (ETA), Uygulamaya özgü tümdevre teknolojileri yaz okulu notları, østanbul,1993. H. Kuntman, øleri analog tümdevre tasarımı: Analog devreler, (Endüstri Semineri Notu), øTÜ øleri Elektronik Teknolojileri Araútırma Geliútirme Vakfı (ETA), østanbul,1994. P.R. Gray, R.G. Meyer, Analysis and design of analog integrated circuits, John Wiley, 1984. R. Gregorian, G.C. Temes, Analog MOS integrated circuits for signal processing, John Wiley, 1986. A.B. Grebene, Bipolar and MOS analog integrated circuit design, John Wiley, 1984. F. Riedel, MOS Analogtechnik, Oldenburg Verlag, Wien, 1988. P.E. Allen and D.R. Holberg, CMOS analog circuit design, Holt, Rinehart and Winston Inc., New York, 1987. W. Sansen, Analog functional blocks, nonlinear analog functional blocks, Swiss Federal Institute of Technology, Intensive Summer Course, 1989.