Veriliş Tarihi: 20.03.2015

Teslim Tarihi: 06.04.2015

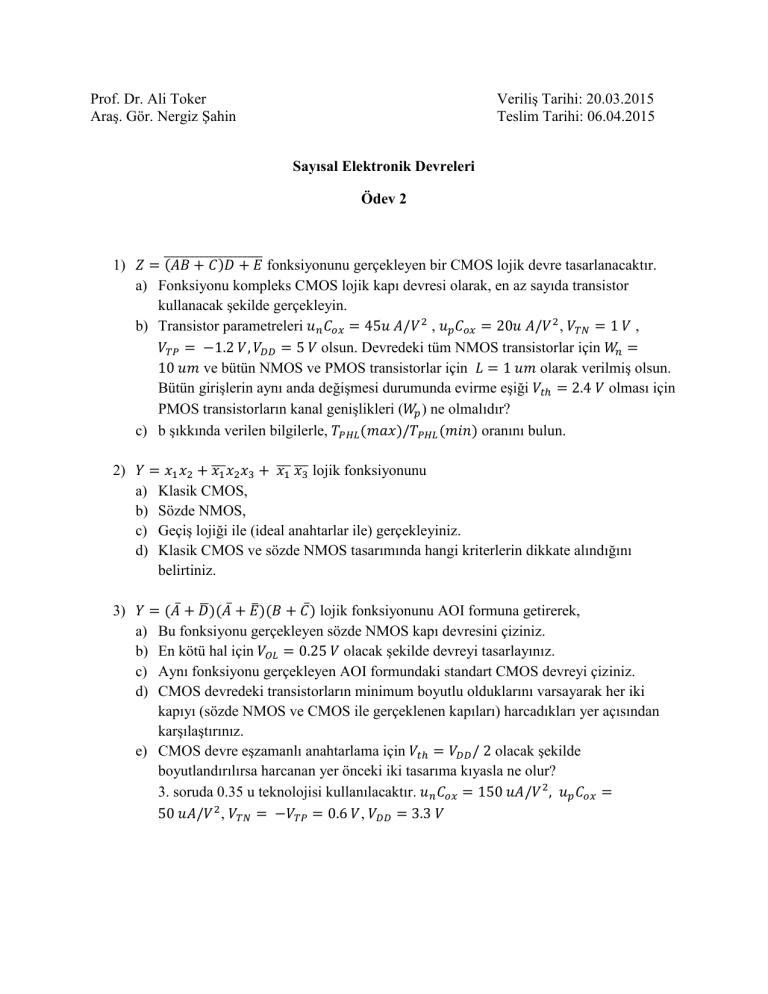

Prof. Dr. Ali Toker

Araş. Gör. Nergiz Şahin

Sayısal Elektronik Devreleri

Ödev 2

(𝐴𝐵 + 𝐶)𝐷 + 𝐸 fonksiyonunu gerçekleyen bir CMOS lojik devre tasarlanacaktır.

1) 𝑍 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

a) Fonksiyonu kompleks CMOS lojik kapı devresi olarak, en az sayıda transistor

kullanacak şekilde gerçekleyin.

b) Transistor parametreleri 𝑢𝑛 𝐶𝑜𝑥 = 45𝑢 𝐴/𝑉 2 , 𝑢𝑝 𝐶𝑜𝑥 = 20𝑢 𝐴/𝑉 2 , 𝑉𝑇𝑁 = 1 𝑉 ,

𝑉𝑇𝑃 = −1.2 𝑉, 𝑉𝐷𝐷 = 5 𝑉 olsun. Devredeki tüm NMOS transistorlar için 𝑊𝑛 =

10 𝑢𝑚 ve bütün NMOS ve PMOS transistorlar için 𝐿 = 1 𝑢𝑚 olarak verilmiş olsun.

Bütün girişlerin aynı anda değişmesi durumunda evirme eşiği 𝑉𝑡ℎ = 2.4 𝑉 olması için

PMOS transistorların kanal genişlikleri (𝑊𝑝 ) ne olmalıdır?

c) b şıkkında verilen bilgilerle, 𝑇𝑃𝐻𝐿 (𝑚𝑎𝑥)/𝑇𝑃𝐻𝐿 (𝑚𝑖𝑛) oranını bulun.

2) 𝑌 = 𝑥1 𝑥2 + ̅̅̅𝑥

𝑥1 2 𝑥3 + ̅̅̅

𝑥1 ̅̅̅

𝑥3 lojik fonksiyonunu

a) Klasik CMOS,

b) Sözde NMOS,

c) Geçiş lojiği ile (ideal anahtarlar ile) gerçekleyiniz.

d) Klasik CMOS ve sözde NMOS tasarımında hangi kriterlerin dikkate alındığını

belirtiniz.

̅ )(𝐴̅ + 𝐸̅ )(𝐵 + 𝐶̅ ) lojik fonksiyonunu AOI formuna getirerek,

3) 𝑌 = (𝐴̅ + 𝐷

a) Bu fonksiyonu gerçekleyen sözde NMOS kapı devresini çiziniz.

b) En kötü hal için 𝑉𝑂𝐿 = 0.25 𝑉 olacak şekilde devreyi tasarlayınız.

c) Aynı fonksiyonu gerçekleyen AOI formundaki standart CMOS devreyi çiziniz.

d) CMOS devredeki transistorların minimum boyutlu olduklarını varsayarak her iki

kapıyı (sözde NMOS ve CMOS ile gerçeklenen kapıları) harcadıkları yer açısından

karşılaştırınız.

e) CMOS devre eşzamanlı anahtarlama için 𝑉𝑡ℎ = 𝑉𝐷𝐷 / 2 olacak şekilde

boyutlandırılırsa harcanan yer önceki iki tasarıma kıyasla ne olur?

3. soruda 0.35 u teknolojisi kullanılacaktır. 𝑢𝑛 𝐶𝑜𝑥 = 150 𝑢𝐴/𝑉 2 , 𝑢𝑝 𝐶𝑜𝑥 =

50 𝑢𝐴/𝑉 2 , 𝑉𝑇𝑁 = −𝑉𝑇𝑃 = 0.6 𝑉, 𝑉𝐷𝐷 = 3.3 𝑉