ELEKTRİK MÜHENDİSLİĞİ

6. ULUSAL KONGRESİ

11 -17 Eylül 1995

BURSA

, TMMOB

I ELEKTRİK MÜHENDİSLERİ ODASI

ULUDAĞ ÜNİVERSİTESİ

MÜHENDİSLİK MİMARLIK FAKÜLTESİ

ELEKTRONİK MÜHENDİSLİĞİ BÖLÜMÜ

TÜBİTAK

ISBN : 9 7 5 - 3 9 5 - 1 5 4 - X

Baskı:

KARE AJANS & MATBAACILIK

Litrosyolu, 2. Matbaacılar Sanayi Sitesi

C Blok No : 4 NC 25 Topkapı - İstanbul

Tel : (0212) 544 09 79 - 544 92 85

o\soz

TMMOB Elektrik Mühendisleri Odası, Uludağ Üniversitesi Mühendislik-Mimariık Fakültesi

Elektronik Mühendisliği Bölümü ve TÜBiTAK'ın işbirliği ile 11-17 Eylül 1995 tarihleri arasında

düzenlenen Elektrik Mühendisliği 6.Ulusal Kongresine hoşgeldiniz.

Hazırlık çalışmaları yaklaşık bir yıl önce başlayan Kongre'ye, Üniversitelerimiz, araştırma ve

endüstri kurumlarında çalışan meslektaşlarımız büyük ilgi göstermiş ve toplam 450 civarında

bildiri başvurusu olmuştur.

Aydınlatma Tekniği, Ar-Ge ve Teknoloji Üretimi, Bilgisayar ve Kontrol, Devreler ve Sistemler,

Elektronik, Elektromagnetik Alanlar ve Mikrodalga Tekniği, Elektrik Makinaları, Elektrik Enerji

Üretimi ve Dağıtımı, Eğitim, Güç Elektroniği, Haberleşme Tekniği ve Sistemleri, Ölçme Tekniği,

Tıp Elektroniği ve Yüksek Gerilim Tekniği konularına göre ayrılan bildiriler, yürütme kurulunca

belirlenen değerlendirme kuralları çerçevesinde uzmanlarca değerlendirilerek, yaklaşık 300

kadarının oturumlarda sunulması uygun bulunmuştur.

Üç Ayrı ciltte toplanan bildirilerin, Aydınlatma Tekniği, Enerji Üretim, İletim ve Dağıtımı,Yüksek

Gerilim Tekniği, Güç Elektroniği, Elektrik Makinaları birinci ciltte, Elektronik, Elektromağnatik

Alanlar ve Mikrodalga Tekniği, Haberleşme Tekniği ve Sistemleri, Ölçme Tekniği, Tıp Elektroniği

ikinci ciltte, Bilgisayar ve Kontrol, Eğitim ve diğerleri üçüncü ciltte yer almıştır.

EMO ve Üniversitelerin temsilcilerinin yanısıra kamu ve özel sektör temsilcilerinin de yer aldığı

Kongre Danışma Kurulu'nca belirlenen görüşler çerçevesinde, Elektrik-Elektronik Mühendisliğini

ilgilendiren çeşitli konularda paneller ve çağrılı bildiriler de düzenlenmiş bulunmaktadır.

Türkiye'de Elektrik-Elektronik Sanayinin Konumu, AB İle Bütünleşmesi ve Perspektifler, ElektrikElektronik Mühendisliğinde Eğitim, Altyapı Hizmetleri Özelleştirme ve Düzenleyici Erk, Türkiye'nin

Elektrik Enerji Sisteminde Yapısal Değişiklikler ve Politikalar konulu paneller ve Bilgi Çağının

Anahtar Teknolojisi; Mikroelektronik, Mikrodalga Enerjisinin Endüstriyel Uygulamaları, Bilgi

Toplumu ve Internet, Elektrik-Elektronik sanayinin Gelişiminde Ar-Ge'nin Önemi, Nükleer Güç

Santrallerinin İşletmesindeki Teknik Sorunlar ve Çevre Konulu çağrılı bildirilerle konuların

tartışılacağı, bilimsel yaklaşımlarla çözüm ve önerilen geliştirileceği, ilgili kurum ve kuruluşlara

önemli katkılar sağlayacağı inancındayız.

Kongrede çağrılı bildiri ve panellere katılarak değerli katkılarda bulunacak değerli bilim adamları

ile özel ve kamu kuruluş yetkililerine sonsuz teşekkürlerimi sunuyorum.

Bugüne kadar iki yılda bir düzenli olarak yapılan, bilimsel niteliği ve katılımı giderek artan Elektrik

Mühendisliği Ulusal Kongresi, Ülkemizde yapılan bilimsel ve teknolojik çalışmaların nitel ve nicel

özelliklerini yansıtması bakımından önem arzetmektedir.'

Kongrenin, izleyiciler ve delegeler için başarılı olmasını, ülkemizin bilimsel ve teknolojik

çalışmalanna yön ve ivme vermesini diliyor, hazırlık çalışmalarımıza özenle katkı sağlayan değerli

TMMOB Elektrik Mühendisleri Odası Yönetim Kuruluna, Elektrik Mühendisleri Odası Bursa Şubesi

Yönetim Kuruluna ve Çalışanlarına, Bilim Kurulu, Danışma Kurulu, Yürütme Kurulu ve Sosyal

İlişkiler Komisyonu üyeleri ile emeği geçen tüm arkadaşlarımıza destek ve katkıları için teşekkür

ediyorum.

Prof. Dr.Ali OKTAY

Yürütme Kurulu Başkanı

ELEKTRİK MÜHENDİSLİĞİ 6.ULUSAL

KONGRESİ

YÜRÜTME KURULU

Prof. Dr.Ali OKTAY

Prof.Dr.Ahmet DERVİŞOĞLU

Prof.Dr.R.Nejat TUNCAY

Teoman ALPTÜRK

Faruk KOÇ

Haluk ZONTUL

Ömer ADIŞEN

EmirBİRGÜN

Sevim OZAK

Yakup ÜNLER

Osman AKIN

H.İbrahim BAKAR

(U.Ü. - Başkan)

i

(İTÜ)

(EMO Başkanı)

(EMO Bursa Şube Başkanı)

(EMO Yön.Kur. Üyesi)

(U.Ü.)

(EMO-Bursa Şube Yön.Kur.Yazman Üyesi)

(EMO-Bursa Şube Yön.Kur. Üyesi)

(EMO-Bursa Şubesi)

(EMO-Bursa Şubesi)

(EMO-Bursa Şubesi)

TMMOB

ELEKTRİK MÜHENDİSLERİ ODASI

BURSA ŞUBESİ YÖNETİM KURULU

Başkan

Başkan Yrd.

Yazman

Sayman

Üye

Üye

Üye

Faruk KOÇ

İsmail Yalçın AKTAŞ

Emir BİRGÜN

Bahri KAVİLCİOĞLU

Sevim ÖZAK

Tuncay HIZLIOĞLU

Cem ÖZKAN

TMMOB

ELEKTRİK MÜHENDİSLERİ ODASI

BURSA ŞUBE GÖREVLİLERİ

Kemal ERTUĞRAN

Kemal KARAKAŞ

Raziye BEĞEN

Meliha DEMİR

Hüseyin GÖK

: Kongre-Fuar Sorumlu Mühendisi

: Proje Denetim ve Test Mühendisi

: Sekreterya Sorumlusu

: Muhasebe Görevlisi

: Şube Görevlisi

SOSYAL ETKİNLİKLER KOMİSYONU

İnci BECEREN

Sabiha CESUR

Bekir DAĞLAROĞLU

Gülsemin GÜNEŞ

Muvaffak KARAHAN

Önder SERHATLI

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- I -

BİLİMSEL DEĞERLENDİRME KURULU

- AKÇAKAYA Ergül, Prof. Dr.(İTÜ)

- AKPINAR Sefa, Prof.Dr. (KTÜ)

• ANDAY Fuat, Prof.Dr.(İTÜ)

- ATAMAN Atilla, Prof.Dr. (YTÜ)

• AYGÖLÜ Ümit, Prof.Dr.(İTÜ)

• AŞKAR Murat, Prof. Dr. (ODTÜ)

• BAYRAKÇI H.Ergün, Prof.Dr.(UÜ)

• BURŞUK A.Fahri, Prof.Dr. (İÜ)

• BİR Atilla, Prof.Dr.(İTÜ)

• CANATAN Fatih, Prof.Dr.(ODTÜ)

•CERİDÖmer, Prof. Dr. (BÜ)

•ÇETİN İlhami, Prof.Dr.(İTÜ)

• ÇİFTÇİOGLU Özer, Prof.Dr. (İTÜ)

• DALFEŞ Abdi, Prof.(İTÜ)

• DEMİRÖREN Ayşen, Yrd.Doç.Dr.(İTÜ)

• DERVİŞOĞLU Ahmet, Prof.Dr.(İTÜ)

• ERTAN H.Bülent, Prof.Dr.(ODTÜ)

• ERTAŞ Arif, Prof.Dr.(ODTÜ)

• ERİMEZ Enise, Prof.Dr. (İTÜ)

FADIL Salih, Yrd.Doç.Dr.(OÜ)

GÖKMEN Muhittin, Prof.Dr.(İTÜ)

GONÜLEREN Ali Nur, Prof.Dr.(İTÜ)

GÜLGÜN Remzi, Prof.Dr.(YTÜ)

GÜNAN Hasan, Prof.Dr.(ODTÜ)

GÜNEŞ Filiz, Prof.Dr.(YTÜ)

GÜRLEYEN Fuat, Doç.Dr.(İTÜ)

GÜVEN Nezih, Doç.Dr.(ODTÜ)

GÜZELBEYOGLU Nurdan, Prof.Dr.(lTÜ)

HARMANCI A.Emre, Prof.Dr. (İTÜ)

İDEMEN Mithat, Prof.Dr.(İTÜ)

İDER Y.Ziya, Prof.Dr. (ODTÜ)

İNAN Kemal, Prof.Dr.(ODTÜ)

KALENDERLİ Özcan, Yrd.Doç.Dr.(İTÜ)

- KASAPOĞLU Asım, Prof.Dr.(YTÜ)

- KAYPMAZ Adnan, Doç.Dr.(İTÜ)

- KORÜREK Mehmet, Doç.Dr.(İTÜ)

- KUNTMAN H.Hakan, Prof.Dr.(İTÜ)

- LEBLEBİCİOĞLU Kemal, Prof.Dr.(ODTÜ)

- MERGEN Faik, Prof.Dr.(İTÜ)

- MORGÜL Avni, Prof.Dr.(BÜ)

-OKTAYAli, Prof.Dr.(UÜ)

- ONAYGİL Sermin, Doç.Dr.(İTÜ)

- ÖNBİLGİN Güven, Prof.Dr.(19 MAYIS Ü)

- ÖZAY Nevzat, Prof. Dr. (ODTÜ)

- ÖZDEMİR Aydoğan, Doç.Dr.(İTÜ)

- ÖZKAN Yılmaz, Prof. Dr.(İTÜ)

- ÖZMEHMET Kemal, Prof.Dr.(9 EYLÜL Ü)

- PANAYIRCI Erdal, Prof.Dr. (İTÜ)

- RUMELİ Ahmet, Prof.Dr.(ODTÜ)

- SANKUR Bülent, Prof.Dr.(BÜ)

- SARIKAYALAR Şefik, Prof.(YTÜ)

- SEVAİOĞLU Osman, Prof.Dr.(ODTÜ)

- SEVERCAN Mete, Prof.Dr. (ODTÜ)

- SOYSAL A.Oğuz, Prof.Dr.(İÜ)

- ŞEKER Selim, Prof.Dr.(BÜ)

- TACER Emin, Prof.Dr.(İTÜ)

- TANIK Yalçın, Prof.Dr.(ODTÜ)

-TARKAN Nesrin, Prof.Dr.(İTÜ)

- TOPUZ Ercan, Prof.Dr.(İTÜ)

- TUNCAY R.Nejat, Prof.Dr. (İTÜ)

- TÜRELİ Ayhan, Prof.Dr.(ODTÜ)

- ÜÇOLUK Metin, Prof.Dr.(İTÜ)

- YAZGAN Erdem, Prof.Dr.(HÜ)

- YÜCEL Metin, Prof. (YTÜ)

- YÜKSEL Önder, Prof.Dr.(ODTÜ)

- YÜKSELER Nusret, Prof.Dr.(İTÜ)

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- II •

DANIŞMA KURULU

- AKÇAKAYA Ergül (Prof.Dr.-İTÜ)

- AKKAŞLI Nevzat

- ALADAĞLI Tunç (Nergis A.Ş.)

- ALGÜADİŞ Selim (EKA)

- ARABUL Hüseyin (EMSAD)

- ARGUN Tanju (TESİD)

- ATALI İbrahim (EMO Adana Şube)

- ATEŞ Mustafa (TEDAŞ)

- AVCI M.Naci (Organize Sanayi Bölgesi)

- BAYKAL Faruk (Nilüfer Belediye Başkanı)

- BERKOĞLU İsmail (PTT Bölge Başmüdürü)

- BOZKURT Yusuf (MEES)

- BİRAND Tuncay (ODTÜ)

- CANER Süleyman (Çanakkale Seramik)

- CEYHAN Mümin

- CEYLAN Arif

- ÇALIM Yavuz (TEAŞ Müessese Müdürü)

- DRAMA Mehmet (TEDAŞ)

- DURGUT Metin (EMO Merkez)

- GÖREN Sunay (Siemens)

- HARMANCI Emre (Prof.Dr.-İTÜ)

- ISPALAR Ayhan (EMKO)

- KAYA Ersin (Kaynak Dergisi)

- KAŞIKÇI İsmail (Almanya)

- KIRBIYIK Mehmet (Prof.Dr.-U.Ü.Müh.Mim.Fak.Dekanı)

- KUZUCU Mehmet (TOFAŞ Elk.Eln.Tesis Servis Şefi)

- MUTAF M.Macit (EMO İzmir Şube)

- OKAT ismail (TEDAŞ Bursa Müessese Müdürü)

- OKUMUŞ Necati(TEDAŞ)

- OKYAY Nursel (TEDAŞ)

- ÖZMEHMET Kemal (Prof. Dr.-9 Eylül)

- ÖNBİLGİN Güven (Prof.Dr.-19 Mayıs Ü.)

- PUCULAOĞLU Mustafa (EMO Merkez)

- RAŞİTOĞLU Mithat (TEDAŞ)

- SÖNMEZ Ali Osman (Ticaret ve Sanayi Odası Başkanı)

- TERZİOĞLU Tosun(TÜBİTAK)

- YAZICI Ali Nihat (EMO Merkez)

- YEŞİL Hüseyin (EMO İstanbul Şube)

- YÜCEL Behçet

- YÜKSELER H.Nusret (Prof.Dr.-İTÜ)

- YURTMAN Naşit (Oyak Renault Fab.Teknik Servis Bakım Müdürü)

- YİĞİT Ali (EMO Ankara Şube)

- ZÜMBÜL İsmail

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- III -

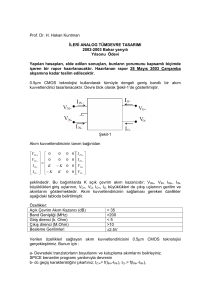

6/Z-H

MİKROELEKTRONİKTEKİ GELİŞMELER VE YİTAL'DE

GELİŞTİRİLEN 3u,m-CMOS PROSESİ

Atilla Ataman

Yıldız Teknik Üniversitesi

Elektronik ve Haberleşme Mühendisliği Bölümü

Maslak istanbul

1. GİRİŞ

Dünya elektronik sanayi pazarı 9O'lı

yılların başından bu yana ortalama

%12'lik bir artış göstererek 1994 yılı

itibariyle yaklaşık olarak 1.1 trilyon

dolara ulaşmış olup, makina ve

otomobil gibi sanayi sektörlerini geride

bırakarak dünyanın bir numaralı pazarı

konumuna

gelmiştir.

Elektronik

sanayinin itici gücünü mikroelektronik

endüstrisi oluşturmaktadır. Şekil. 1.1'de

dünya yarıiletken ve tümdevre (IC)

pazarının gelişimi görülmektedir.

1"

60

3

40

20

0

BIPOLAR HAFIZA

90-

^ | ANALOG

80 •

BIPOLAR

LOJIK

^ ^ ^ H

y^

60

| T U MD E VR E

PAZARI

•

GaAs ve DİĞERLERİ

100

70 J

D U N Y A

YAR11LE TK EN

P A Z A R I

200

180

160

o 140

o 120

a

100

S 80

1994 yıllarında ortalama artış %30 lar

düzeyinde

olmuştur.

Yarıiletken

pazarının %85'ini oluşturan tümdevre

(IC) payının asrın sonunda %90 lara

ulaşması beklenmektedir.

Dünya ticari tümdevre pazarının

ürünler açısından dağılımı Şekil.2'de

verilmektedir.

j MOS LOJIK

"i

50

•JTOPLAM

P AZAR

--

-,1i

1

ili 3 1 1

rutini

lıil

40

30 •

20 •

Şekil. 1.1:DünyaYarıiletken ve tümdevre

pazarlarının yıllara göre değişimi

1 MOS HAFIZA ^ ^ H

10 •

0 •

1980 li yılların basıdan itibaren ağırlıklı

olarak silisyum tümdevre üretimine

yönelen yarıiletken pazarı 1994 yılında

100 milyar doları aşmış olup 2000 li

yılların başında 200 milyar dolara

ulaşması beklenmektedir. 1993 ve

1982($10BI

1

•

1996IJ115B

Şekil. 1.2:

Dünya ticari tümdevre

pazarının ürünler açısından dağılımı.

* TÜBİTAK Marmara Araştırma Merkezi Ulusal Elektrontt- Lnstitüsü Danışmanı

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 462 -

%30 düzeyinde pazar payını oluşturan

MOS-bellek ve özellikle %20 lik pazar

payı ile DRAM, yarıiletken teknolojisinin

boyut ve tümleştirme yoğunluğu

açısından öncü rolünü üstlenmektedir.

Şekil. 3.'de tümdevrelerdeki gelişimin

kullanılan teknoloji açısından değişimi

verilmektedir. 1980 li yılların başından

itibaren ağırlık, bipoiar teknolojisinden

MOS ve özellikle komplementer MOS

yapı olarak bilinen, PMOS ve NMOS

elemanlarının

kullanıldığı

CMOS

teknolojisine

kaymıştır.

Bipoiar

teknolojisinin yarıiletken pazarındaki

payı, gelecekte %10 lar düzeyinde

doyma eğilimi göstermektedir.

ECL

GaAs

100

1982

(S10B)

Şekil. 1.3:Kullanılan teknoloji açısından

dünya pazarının zaman içinde değişimi.

2. TEKNOLOJİK GELİŞME

Tümdevre teknolojisi 6O'lı yılların

başında bipoiar analog devrelerin

üretimi

ile

başlamıştır.

1970'te

yoğunluğu

1

Kbit olan

PMOS

teknolojisiyle üretilen bellekler INTEL

tarafından piyasaya sürülmüştür. 1968

yılında Denard tarafından bulunan tek

transistorlu DRAM hücre yapısının

kullanıldığı 4K bit bellekler 1972 yılında

aynı firma tarafından üretilmiş ve

teknolojinin minimum boyutu 8 ^m

olarak gerçeklenmiştir. 1970'li yılların

ortalarında başlayan teknoloji yarışı bir

silisyum kırmığı (chip) üzerinde en

küçük boyutlu ve en yüksek yoğunluklu

devrelerin

oluşturulmasına

yönelik

olarak sürdürülmektedir. Teknolojinin

öncülüğünü, periyodik bir yapıya sahip

olması ve yüksek pazar payı nedeniyle

DRAM lar yapmaktadır. DRAM'ların

bellek kapasiteleri ve minimum desen

boyutunun (NMOS yapısının kanal

uzunluğu) yıllara göre gelişimi ve

öngörülen gelişme süreci [1] Tablo. 2.1

de verilmektedir.

Kırmık alanı 16 Kbit DRAM lar için 16

mm2 den 64 Mbit için 190 mm 2 ye

genişlemiştir ve 64 Gbit için 1400 mm2

olacağı tahmin edilmektedir. Bunun

doğal sonucu olarak Si-pul çapları

günümüz teknolojisindeki 150-200 mm

den gelecekte 300-400 mm boyutuna

ulaşacaktır. Buna paralel olarak üretim

teknolojilerinde,

yeni

yöntemlerin

geliştirilmesi, yeni cihazların üretilmesi

ve uygun malzemelerin kullanılması

zorunlu olmaktadır.

2.1. Silisyum Tümdevre Teknolojisi

Tümdevre teknolojisi tasarım ve

üretim olmak üzere iki bölümden

oluşmaktadır.

Tasarım

teknoloji

seçimine

bağlı

olarak

(NMOS,

BİPOLAR, CMOS, BİCMOS) mevcut

devre elemanı ve devre bloklarına ait

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 463 -

1976

Yıl

Bellek

16 K

Kapasitesi

5

Min Boyut (pm)

1980

1983

1986

1989

1992

1995

2001

2004

2007

2010

64 K

2

256 K 1 M

1.2

1.6

4M

0.8

16M

0.5

64 M 256 M 1 G

0.35

0.25 0.18

4G

0.13

16 G

0.10

64 G

0.07

1998

Tablo 2.1: DRAM kırmıklarında bellek kapasitesi ve minimum boyutun yıllara göre

değişimi.

bilgisayar ortamında depolanmış venleri

kullanarak , uygun yazılımlarla istenen

devrenin; a) tasarlanması, b) devre

simülasyonunun yapılması ,c) kırmık

üzerine

yerleşim

planlarının

hazırlanması (layout) , d) bağlantı

kapasite ve dirençlerini de kapsayan

ikinci bir simülasyonun yapılması (postlayout

simulation)

adımlarından

oluşmaktadır. Üretim ise yerleşim

planlarına göre üretilmiş maskeler

yardımıyla Si pul üzerine selektif ve

ardışıl olarak uygulanan a) oksitleme,

b) katkılama , c) katman oluşturma d)

katman aşındırma ve e) litografi

işlemlerinden oluşmaktadır. Oksitleme

Si pulun oksijen veya su buharı

ortamında yüksek sıcaklıkta doğrudan

oksitlenmesidir. Katkılama, Si taban

malzemesinin

iletkenlik

değişimini

sağlamak amacıyla, iyon ekme ve/veya

difüzyon

yöntemleri

ile

yabancı

atomlarla ( B, P, As ) katkılanması

olarak

tanımlanmaktadır.

Katman

oluşturma, Si pul üzerinde. Kimyasal

buhardan

depolama (CVD) veya

tozutma (PVD) yöntemleri ile istenen

katmanların oluşturulması süreçlerini

içermektedir.

Si tümdevre teknolojisinde kullanılan

temel katmanlar yalıtım, maskeleme ve

pasivasyon amaçlı kullanılan SiO2 ve

Sİ3N4 katmanları, geçit malzemesi

olarak kullanılan polisilisyum, kontak ve

bağlantı iletkeni olarak kullanılan Al dan

oluşmaktadır.

Katman

aşındırma,

katmanların sıvı kimyasal malzemeler

kullanılarak

(ıslak aşındırma) veya

plazma ortamında tutularak (kuru

aşındırma) selektif olarak alt katmana

kadar

aşındırılması

işlemini

kapsamaktadır.

Litografi,

yukarıda

belirtilen bu süreçlerin selektif olarak

gerçeklenmesi, diğer bir deyimle

istenen desenlerin Si-pul yüzeyinde

oluşturulması için kullanılan süreçtir. Bu

amaçla Si-pul fotorezistle kaplanır,

adım hizalayıcı (stepper) ile öngörülen

maske kullanılarak ışıklandırılır ve

banyo edilerek rezist üzerinde istenilen

desen oluşturulmuş olur.

Üretim

sürecinde kullanılan maske sayısı

teknoloji seçimine bağlı olarak 6-18

arasında

değişmektedir.

Süreç

adımlarının sayısı 400 'lere kadar

çıkmaktadır.

Pul üzerinde oluşturulan tümdevreler

test

edilikten

ve

çalışmayanlar

işaretlendikten sonra kesilir ve kılıflanır.

Kılıflama sonrası tekrar test edilen

tümdevreler piyasaya sürülür.

3.

TÜBİTAK

GELİŞTİRİLEN

M.A.M.

YİTAL'DE

CMOS SÜRECİ

1980 li yılların başında, jonksiyon

izolasyonlu bipolar devrelerin üretimi ve

araştırılması amacına yönelik olarak

Marmara Araştırma Merkezi içinde

Yarıiletken

Teknolojisi

Araştırma

Laboratuarı

(YİTAL) kurulmuş ve

ülkemizde ilk olarak bu laboratuarda

analog tümdevreler üretilmiştir. 1988

yılında "NATO Science for Stability

Programme" tarafından desteklenen,

bir proje ile

CMOS teknolojisine

geçilmiştir. Proje TÜBİTAK, İTÜ ve

TELETAŞ işbirliği ile gerçeklenmiştir

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 464 -

[ 2 ] . Proje istanbul Teknik Üniversitesi

Elektrik Elektronik Fakültesi öğretim

üyelerinden Prof. Dr. Duran Leblebici

tarafından

yürütülmüştür.

Proje

süresince

24

araştırıcı

katkıda

bulunmuştur. Laboratuarın pul işleme

kapasitesi 3 inch'den 4 inch'e

yükseltilmiş, CMOS süreci için gerekli

ek teçhizat (iyon ekme cihazı, düşük

basınçlı kimyasal buhardan depolama

cihazları

-LPCVD-,

reaktif

iyon

aşındırma cihazları ve adım hizalamalı

aydınlatma cihazı -STEPPER- ) satın

alınmış, kurulmuş ve çalıştırılmıştır.

Projenin amacını temel olarak, endüstri

standardında 3 (am minimum geometrili

CMOS-VLSI tümdevrelerin üretimine

olanak verecek bir prosesin a) simüle

edilmesi oturtulması, optimizasyonu ve

test edilmesi b) devre yapılarına ait veri

kütüphanelerinin oluşturulması ve yerel

endüstrinin hizmetine sunulması, c)

prototip ve pilot üretim hizmetlerinin

karşılanması

ve d)daha küçük

geometrili

CMOS

teknolojilerine

geçmek için gerekli ön çalışmaların

yapılması, şeklinde özetleyebiliriz.

3.1) Geliştirilen 3um CMOS Süreci

YİTAL de düşük katkılı p-tipi silisyum

pul kullanılarak n-kuyulu CMOS prosesi

gerçeklenmiştir.

CMOS

hücresinin

NMOS transistoru doğrudan taban

malzeme

üzerinde

gerçekleşirken

PMOS

transistor

yapısı

p-taban

malzeme içinde, iyon ekme ve

difüzyonla oluşturulan ve böylece

tabandan

yalıtılmış

olan

n-kuyu

bölgesinde

gerçekleştirilmektedir.

Şekil.3.1'de bu şekilde oluşturulmuş bir

CMOS yapısının şematik gösterimi ve

YİTAL de gerçekleştirilen 3^m-CM0S

sürecinin

üretim

adımları

gösterilmektedir. Verilen şekiller CMOS

yapısına ait kesitin uygulanan süreç

adımları ile değişimini vermektedir.

Üretim sürecinde 9 farklı maske

kullanılmıştır. Sürece geçilmeden önce

tasarım kuralları oluşturulmuş, bu

kurallara göre test yapıları çizilmiş ve

maskeleri üretilmiştir. Maskeler, Si- pul

yüzeyinde istenen desen aktarımını

sağlayacak 5cm x 5cm boyutunda 1.5

mm kalınlığındaki cam levhalardır.

Yüzeyi ışığa duyarlı bir emülsyonla

kaplı bu maske camları bilgisayar

kontrollü bir x-y tezgahı üzerine

yerleştirilip bölgesel olarak ışıklandırılıp

banyo edilerek istenilen desenler

oluşturulur.

Maske

üzerinde

oluşturulmuş bu desenler daha sonra

adım hizalayıcılarla, optik olarak Si-pul

yüzeyinde bulunan fotorezist tabakalara

aktarılırlar. Pulun banyo edilmesi ile

maske deseni pula aktarılmış olur.

Test yapıları, farklı eleman ve devre

yapılarına ait parametrelerin elde

edilmesi,

tasarım

kurallarının

geçerliliklerinin incelenmesi, güvenirlik

ve proses karakteristiklerinin (tabaka

direnci , kontak direnci, basamak örtme

özellikleri

v.b)

analizi

için

oluşturulmuşlardır. Şekil 3.1 de sürecin

anlaşılması açısından süreç adımları

ayrıntılı olarak verilmiştir. Şekillerin

incelenmesinden

görüleceği

üzere

tümdevre üretim süreci genelde 2.1 de

belirtilen

5

temel

işlemden

oluşmaktadır.

SUPREM simülasyon paketi ile

istenen eşik gerilimleri ve sınır değerler

için proses parametreleri ( difüzyon

süreleri ve sıcaklıklar, iyon dozları ve

enerjileri , oksitleme süreleri ve

sıcaklıkları , geçit oksiti kalınlığı v.b.)

belirlendikten sonra üretim süreci

gerçeklenmiş ve test yapıları ile proses

değerlendirilmiştir. Üç üretim süreci

sonunda proses, öngörülen eleman ve

devre özelliklerini verecek şekilde

optimize edilmiştir. Prosesi endüstriyel

tasarıma sunmak amacıyla PMOS ve

NMOS

transistörlerin

SPICE

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 465 -

n-kuyu -

P'-K /S

is

!_>__] i

7) Saçılma Oksidi. dox= 20 nm. T= 1000 °C

Akili Solgf

; Polisıiısyum

(cm)'' ;

E = 150keV

o -loban (100)

8) Kuyu Implantasvonu

1) Yüzey ı emızieme

'

//'////////////////////////.'.

'/•'•',

••••//,

Â

Sı

û.

9) ı emızleme

2) Oksitleme, d, = 0.8 um. T= 1125

5'0,

1

)

•'••"/////..-••'.•.•V;/A S,0,

10) Kuyu Dıfüzyonu. dn= 3.5 um. T= 1125 °C

ı

3) n-kuyu Şekillendirme

s.o.

11) Oksit Silme

Sı 0 ,

4) Banyo

12) Taban Oksidi, dox= 50 nm. T= 1000 °C

V//1

, — ,

A

. , - . • • - • • • . — — - — - - — ;

/ 5) Oksit Aşındırma

:

s,o,

13) Nitrıt Büyütme. dn= 150 nm. T= 800

5) Rezıst Silme

Şekil.3.1: YİTAL 3(jm CMOS

Tümdevre Üretim Akısı

14) Aktif Bölge ŞeKillendırmesı

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 466 -

s.,.«

5.0,

s.

23) Nitrit Silme. H,PO4 , T = 150 °C

15) Banyo

so,

24) Oksit Silme

16) Nitrıt Aşınaırma: C F I + O:

25) Saçılma Oksidi, dox= 425 nm T= 1000 °C

17) Alan Implantasyonu Şekillendirme

İ

l

i

1

= 5.5 10' (cm)"

Pft

S.,N.

t

2

I

;

I

I

E = 25 keV

Sı 0.

s.o,

26) Eşik implantasyonu

18) Banyo

I

D = 2.3 10

(cm)'' :

t

>

I

S'

E = 25 keV

\sı

S..N.

S.O:

27) Oksit Silme

19) Alan implantasyonu

SıC,

28) Geçit Oksidi, dox= 42.5 nm T= 1000 °C

20) Katkı Dağılımı

S,, N.

s, o,

i s,

21) Rezıst Silme

Sİ,N 4

S.O.

22) LOCOS-Prcsesı, üox= 0.6 um, ~= 900 °C

29) Polisilısyum û^x= 500 nm T= 500 °C

K

30) Polisilısyum Katkılama, T= 1000 °C

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 467 -

37) Katki Dağılımı

31) Polı Şekillendirme

ı

-?

PR

"olmlrsyurr

S, C,

38) Rezıst Silme

\

32) Banvo

Polıtıitsyum

39) NMOS S/K Şekillendirme

33) Poii Aşındırma. SF6 * Q2

40) Banyo

i

I

i

ı£

I

D = 6 1C (cm)-

2

I

;

ı

i

i

E=150keV

34) PMOS S/K-Sekillendırme

41) NMOS S/K impiantasyonu

= 2.5 10 15 (cm)" 2 ;

36) PMCS S/K İmplantasyonu

43) Oksit Büyütme. dn= 1 um T= 360 CC

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 468 -

As

50) Banyo

44) KontaK Şekilendırme

Al-Aşındırma; CHF3 + Cl2 + BCI3

45) Banyo

46) Oksit Aşındırma: CHF3 + O,

47) Rezıst Silme

52) Rezıst Silme

53) Koruyucu Oksit. d3OIİ= 1 um, T= 360 °C

48) AI-KaDlama: d A , = 1um

54) Pabuç Şekillendirme

49) Al-Şekiilendirme

55; Rezıst Siime

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 469-

parametreleri çıkarılmış, devre yapıları

ile ilgili kütüphaneler oluşturulmuş ve

ilgilenen kurumlara sunulmuştur 3;.

Proje bünyesinde YİTAL tümdevre

tasarım

gurubu

oluşturulmuş

ve

EUROCHIP'

adlı

Avrupa

birliği

bünyesinde bulunan bir organizasyona

üye olunmuştur.

4. SONUÇ

1) Ülkemizde ilk olarak tek metal tek

polisilisyum

katmanlı,

endüstri

standartlarında analog ve dijital VLSI

devre tasarımı ve üretimine olanak

verecek 3um minimum geometriye

sahip bir CMOS prosesi geliştirilmiş,

gerekli veri kütüphaneleri CADENCE

yazılım

ortamına

aktarılmış

ve

endüstrinin hizmetine sunulmuştur.

2) VLSI tasarım, süreç simülasyonu ve

üretim

konularında

bilgi

birikimi

oluşmuş ve önemli bir deneyim

kazanılmıştır.

3) Endüstriyel prototip üretim sürecine

girilmiş ve bu amaçla bir tanesi SİMKO,

iki tanesi NETAŞ için olmak üzere

toplam 9 tümdevre kırmığı üretilmiş ve

test edilmiştir.

4) İstanbul ve çevresinde bulunan

yüksek öğretim kurumlarının elektronik

mühendisliği bölümlerinde özellikle

yüksek

lisans

ve

doktora

programlarında mikroelektronik önem

kazanmaya başlamıştır.

5) Kazanılan bu deneyimler sonucunda

1994 yılı sonunda dört büyük endüstri

kuruluşunun

(ALCATEL-TELETAŞ,

NETAŞ, BEKO, SİMKO) doğrudan

katkıları, İstanbul Teknik Üniversitesi ve

İTÜ-ETA vakfının katılımı ve NATO

desteği ile yeni bir proje ( TU

MICROFAB II ) başlatılmıştır [ 4 ] . Bu

proje ile 1.5 (.im minimum geometrin iki

poli ve iki metal katmanlı CMOS

teknolojisinin

gerçeklenmesi

hedeflenmiştir. 1995 yılı başında süreç

tasarımı yapılmış, proses performansını

saptamak ve 1.5 um standart hücre

parametrelerini oluşturmak amacıyla iki

test kırmığı tasarlanmış maskeleri

üretilmiş ve ilk deneme sürecine

başlanmıştır. Bu arada YİTAL için

gerekli bir taramalı elektron mikroskobu

, bir düşük basınçlı CVD reaktörü . bir

tozutma cihazı ve plazma destekli oksit

büyütme reaktörü sipariş edilmiş olup

yıl sonunda tüm cihazlar devreye girmiş

olacaktır.

KAYNAKÇA

İM The National Technology Roadmap

for

Semiconductor,

Report

of

Semiconductor Industry Association

1994.

121 Silicon LSI/VLSI Circuits Fabrication

Technologies NATO-TU MICROFAB.

NATO Science for Stabılity (SfS)

Program

Project Plan. September

1987. Gebze.

121 Silicon LSI/VLSI Circuits Fabrication

Technologies Final Report. NATO-TU

MICROFAB December. 1991, Gebze.

IAI 1.5 Micron CMOS-ASIC Fabrication

Technology NATO-TU MICROFAB II,

NATO SfS Program Project Plan,

December 1993, Gebze.

Prof. Dr. Atilla ATAMAN

Federal Almanya'nın

Braunschweig Teknik

Üniversitesi'nden 1968

yılında Yüksek Mühendis

ve 1973 yılında Dr. Müh.

unvanını almıştır. 1973-1985 yılları

arasında K.T.Ü bulunmuştır. 1985

yılında Yıldız Teknik Üniversitesinde

profesörlüğe

yükseltilmiş

ve

bu

kurumda çalışmaktadır. Aynı zamanda

1986 yılından bu yana YİTAL'de

danışman olarak görev yapmaktadır.

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 470-

TÜBİTAK MAM YİTAL 3nm CMOS Tümdevre Üretim Süreci

Optimizasyonunda İzlenen Farklı Yaklaşımların İrdelenmesi

Aziz Ulvi ÇALIŞKAN, Yaman ÖZELÇİ

TÜBİTAK Marmara Araştırma Merkezi

YİTAL 41470 Gebze KOCAELİ

ÖZET :TÜBİTAK Marmara Araştırma

Merkezi Ulusal Elektronik ve Kriptoloji

Enstitüsü

Yarıiletkenler

Teknolojisi

Araştırma

Laboratuarında (YİTAL)

yürütülen

"VLSI/CMOS

Tümdevre

Teknolojisi

Geliştirilmesi

ve

Uygulanması" projesi ile tek metal tek

poli-silisyumlu 3 um CMOS tümdevre

üretim süreci geliştirilmiştir. MOS

tranzistorların kanal bölgelerinin iyon

ekme tekniği ile katkılanma işlemi biri

geçit oksidi üzerinden, diğeri geçit

oksidi büyütme öncesi ön oksit

üzerinden olmak üzere iki farklı

yöntemle gerçeklenebilir. Bu makalede

YİTAL'de geliştirilen alternatif iki süreç

ile üretilen NMOS ve PMOS tranzistorlarının karakteristikleri tanıtılacaktır.

de maruz kalır. Bu durum, üretilecek

tümdevrelerin sağlam ürün oranını ve

güvenilirliklerini düşürecek yönde etki

yapar.

YİTAL'de kullanılan türde bir

orta-akımlı iyon ekme cihazının pul

yükleme ve boşaltma sisteminde, pul

yüzeyinde oluşan 0.5 um ve daha

büyük

partikül sayısı işlem başına

ortalama 100 kadardır İM. iyon ekme

süreci sırasında oluşan bir diğer etki

ise metalik kirlenmedir. Yüksek enerjili

iyonlar cihazın içindeki metal aksama

çarpar ve bu yüzeylerde oluşturduğu

tozutma (sputter) ile pul yüzeyinin Cu,

Mo, Na, K, Fe, Cr, Ni gibi elementlerle

kirlenmesine neden olur 121.

2-MOS YAPISI :

1İYON

EKME

SİLİSYUM

PULUN

NEDENLERİ:

TEKNİĞİNDE

KİRLENME

CMOS tümdevre üretim sürecinde taban malzemesi olarak kullanılan

silisyum monokristaiine yapılan katkılamalarda iyon ekme tekniği kullanılır.

Bu teknikte silisyuma katkılanacak

pozitif iyonlar (çoğunlukla bor, fosfor

veya arsenik) gerekli olan dalma

derinliğini sağlayacak şekilde (25200kV) gerilim altında hızladırılarak

kristal içine ekilir. Bu işlemde enerji

yüklü

iyonların

silisyum yüzeyine

çarparak

oluşturdukları

kristal

hasarlarının giderilmesi yüksek sıcaklık

(900 - 1100 °C) işlemi ile gerçeklenir.

İyon ekme süreci sırasında silisyum

kristali partikül ve metalik kirlenmeye

YİTAL'in 3um CMOS tümdevre

üretim süreci fotolitografi, plazma

destekli aşındırma, gaz fazdan film

depolama ( chemical vapor deposition,

CVD ), yüksek sıcaklıkta oksitleme ve

iyon ekme gibi tekniklerin belli bir sırada

uygulandığı toplam 59 işlemden oluşur.

Tümdevre üretimde tranzistorların

elektriksel karakteristiklerini,

sürecin

tekrar

edilebilirliğini ve

-güvenilirliğini belirleyen işlemlerden en

önemlileri, MOS yapısı adı altında

gruplananlardır. NMOS ve PMOS

tranzistorların

eşik

gerilimlerinin

hedeflenen

değerlere

ayarlanması

işlemi, tranzistorların kanal bölgelerine

bor iyonu ekimi ile gerçeklenir. Bu iyon

ekme işlemi geçit oksidi üzerinden

yapılabileceği gibi, geçit oksidi büyütme

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 471 -

öncesi pul yüzeyinde oluşturulan bir ön

oksit üzerinden de gerçeklenebilir. Bu

iki farklı üretim tarzına göre YİTAL'de iki

alternatif

3

um

CMOS

süreci

geliştirilmiş ve tümdevre üretimine

uygulanmıştır. Şekil-1a ve şekil-1 b de

bu süreçlere ait işlem akışı silisyum pul

kesitlerini göstererek verilmiştir.

Geçit oksidi üzerinden

kanal

katkısının oluşturulduğu süreçte (C1A)

bor iyonlarının silisyum içindeki profili,

iyon ekmeyi izleyen bir oksitleme işlemi

olmadığından sığ ve diktir. Dolayısı ile

bu süreçle üretilen tranzistorların gövde

etkisine bağımlılığı düşük kalmaktadır.

Buna karşın kanal katkısı sırasında 25

keV'luk bir enerji ile 42.5 nm

kalınlığındaki geçit oksidine çarpan bor

iyonları oksitin yapısında bozulma

oluşturacağı gibi oksidin yüzeyinde

daha önce belirtildiği gibi partikül ve

metalik

kirlenme

de

meydana

gelecektir. İyon ekme işleminden sonra

yapılan kimyasal temizleme işlemi

( RCA ) ile kirlenme en azda tutulmaya

çalışılır.

Kanal katkısının

bir ön oksit

üzerinden yapıldığı C1B sürecinde,

geçit oksidi doğal olarak partikül ve

metalik

kirlenmeye

maruz

kalmayacaktır. Bu yöntemde, 1000

°C'de gerçeklenen geçit oksidi büyütme

süreci sonunda :

a) sığ bor katkısı yüzeyden taban içine

doğru yayılıp genişler,

b) bor atomlarının silisyumdiokside

kaçması sonucu silisyum yüzeyindeki

katkı yoğunluğu azalır.

Kanal

katkısının

yayvanlaşması

tranzistorun eşik geriliminin gövde

etkisine bağımlılığını arttırdığı gibi

yüzeyde

bor

atomlarının

okside

kaçması sürecin tekrar edilebilirliğini

düşürür.

C1A ve C1B için bahsi geçen

tüm etkiler göz önünde bulundurularak

gereken süreç tasarımları gerçeklenmiş

ve test tümdevre üretimine uygulanmıştır. Her iki süreç de NMOS ve

PMOS tranzistorlarının eşik gerilimlerinin simetrik ve sırasıyla 0.75V ve 0.75V olarak hedeflen-mesinin yanı sıra

savak/kaynak bölgeleri belverme ve

tranzistor

erişme

(punch-through)

gerilimlerinin, ayrıca takılma (latch-up)

olayının 5V'luk besleme gerilimine

uygun olacak şekilde gerçeklenmesi

için süreç parametreleri ayrı ayrı

optimize edilmiştir. C1A ve C1B

süreçleri için uygulanan işlem koşullan

Tablo-I'de özetlenmiştir. Her iki süreç

için de 1 5 - 2 5 Q.cm özgül dirençli p

tipi < 100 > yönelimli silisyum pul

kullanılmıştır.

SÜREÇ

1)n-Kuyu iyon ekimi

Fosfor Dozu (cm"2)

2)n-Kuyu Derinleştirme

Sıcaklığı (°C)

3)n-Kuyu Derinleştirme

Süresi (h)

4) Eşik Ayar İyon Ekimi

Bor iyon Dozu (cm'2)

5) Eşik Ayar İyon Ekimi

Enerjisi (keV)

C1A

C1B

3 10' 2

2 10' 2

1125

1160

30

20

5.5 10 : 1

8 10 11

25

45

TablO-l: C1A ve C1B Süreçlerinde

Koşullarda Gerçekleştirilen Adımlar

Farklı

Tablo-I'den görülebileceği gibi

C1A ve C1B süreçlerinde n-kuyu iyon

ekme işleminde, fosfor dozu ile n-kuyu

derinleştirme

sıcaklığı

ve

süresi

değiştirilmiştir. MOS yapısı oluşturma

grubunda ise eşik ayarı için kullanılan

bor katkı dozu ve enerjisi farklı olarak

seçilmişlerdir. Bu parametre gruplamalarına göre üretilen tranzistorların ölçüm

sonuçları Tablo-ll de verilmiştir.

Şekil-2'de her iki süreçle üretilen

NMOSve PMOS tranzistorlarının eşik

gerilimlerinin mutlak değerlerinin VV/L

oranına göre değişimi verilmiştir.

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 472-

-£f\m- ••

SiO,

Si Taban

a) Yerel Oksitleme Sonrası Si 3 N 4

Filmin Yüzeyden Silinmesi

a) Yerel Oksitleme Sonrası Si 3 N 4

Filmin Yüzeyden Silinmesi

(+B11) Doz: 8E11 cm' 2 E: 45 keV

b) Geçiş Oksidi Üzerinden Eşik

Ayarı için İyon Ekimi

b) Geçiş Oksidinin Yüzeyden

Silinmesi

c) Geçiş Oksidinin Silinmesi,

c) Geçit Oksidinin Büyütülmesi

( + B 11 ) Doz: 5.5E11 cm"2 E: 25 keV

^^^ ^^^ ^^^ ^^^ ^^^ ^^^ ^^^ ^^^ ^^^ ^^^

d) Geçit Oksidi Büyütülmesi,

•

Poli-Silisyum

e) Poli-silisyum Film Depolanma

ve Şekillendirilmesi

Şekil -1a Ön Oksidi Üzerinden

Eşik Ayar Ekimi ile Gerçeklenen

Üretim Akışı (C1B)

d) Geçit Oksidi Üzerinden Eşik

Ayarı için İyon Ekimi

e) Poli-silisyum Film Depolanma

ve Şekillendirilmesi

ŞekiMb Geçit Oksidi Üzerinden

Eşik Ayar Ekimi ile Gerçeklenen

Üretim Akışı (C1A)

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 473-

3|jm/3(jm

NMOST

3jjm/3Mm

PMOST

Parametre

V-o (V)

V^o Std. Sap.

GamafV")

V^o (V)

V^o Std. Sap.

Gama (V' v )

C1A

0.87

0.05

0.15

-0.94

0.03

0.75

C1B '

0.62

0.03

0.32

-0.87

0.05

0.55

Tablo-ll C1A ve C1B Süreçleri ile Üretilen

3 j m/3 M m NMOST ve PMOST Ölçü Sonuçları.

•C1 ANMOS

-C1APMOS

• C'BPMÛS

"M E O E F

değerin

üzerindedir.

n-kuyu

katkılamanın değeri düşürülerek bu

fazlalık

düzeltilebilinirsede

sürecin

takılma

olayına

dayanıklılığı

göz

önünde tutularak değerin düşürülmemesine karar verilmiştir.

Sonuç olarak iki farklı yaklaşımla

YİTAL'de birbirine alternatif iki adet

3um CMOS süreci optimize edilmiştir.

C1A süreci 3 adeti yerel haberleşme

endüstrisinin istemi ile olmak üzere

toplam 9 adet Uygulamaya Özgü

Tümdevre (ASIC) üretimine başarı ile

uygulanmıştır.

Kaynakça:

İM T.R. Carducci, B. Hardegen,

"lon Implanter Upgrade Improves IC

Yields"Microelectronics Manufacturing

Technology January 1991

121 F. Sinclair, J. Blake. B. Simonton,

"Contamination in lon Implanter"

European Semiconductor Nov. 1993

0.6

O.5

3\2 7

3\9

3\3

9\3

27\3

ŞekİI-2 : C1A ve C1B süreçleri ile üretilen

tranzıstorların çeşitli W/L oranları için eşik

geriliminin mutlak değerinin değişimi.

3- SONUÇLAR:

C1B süreci ile üretilen NMOS

tranzistorun

gövde

kutuplamasına

bağımlılığı (Gama:0.32 V1/2), C1A

süreci

ile

üretilen

NMOS

tranzistorunkinden (Gama:0.15 V1/2)

büyüktür. Bu C1B sürecinde kanal

katkısının derinleştiği sonucunu verir.

Fakat ölçülen değer kabul edilebilir

sınırın altındadır. Bu durum eşik ayar

iyon ekme işleminden sonraki toplam

ısıl işlem miktarının düşük tutulmaya

çalışılması ile sağlanmıştır.C1A süreci

•ie uretıien PMOS tranzistorunun

ı 0 75 ıV1'2) olup kabul edilebilir

Aziz Ulvi Çalışkan

1982 yılında İTÜ ElektrikElektronik Fakültesinde

lisansını ,1984 İTÜ Fen

Bilimleri Enstitüsünde

yüksek lisansını tamamladı.

1983 yılından itibaren

YİTAL'de iyon ekme. CVD

teknikleri konusunda araştırmacı

olarak çalışmaktadır.

Yaman ÖZELÇİ

1988 yılında İTÜ ElektrikElektronik Fakültesinde

lisans, 1991 'de ise İTÜ

Fen Bilimleri Enstitüsünde

yüksek lisans eğitimini

tamamladı. 1990 tarihinden

itibaren YİTAL'de tozutma

ve tümdevre testi konularında

araştırıcı olarak çalışmaktadır.

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 474 -

TÜBİTAK MAM YİTAL 3\ım CMOS STANDART HÜCRE KÜTÜPHANESİ VE

NETAŞ İÇİN İKİ UYGULAMAYA ÖZGÜ TÜMDEVRE ÜRETİMİNDE KULLANIMI

Engin KONUR, İ. Can ÇEVİKBAŞ

TÜBİTAK MAM YİTAL Gebze 41470 KOCAELİ

Özet: Hem kişisel bilgisayar (PC)

hem de işistasyonu (vvorkstation)

ortamları için, YİTAL'de 3 um CMOS

Standart

Hücre

Kütüphanesi

hazırlanmıştır.

Bu

kütüphane

kullanılarak, NETAŞ için, iki adet

Uygulamaya Özgü Tümdevre (ASICApplication

Specific

Integrated

Circuit) YİTAL'de tasarlanmış ve

üretilmiştir.

2.1. Şematik Tasarım

Şematik çizim OrCAD'in DRAFT

programıyla yapılır. Tasarımcı giriş

program ayarında (set-up), YİTAL

sembol kütüphanesi için yitalscl ;b'

ve yitalsc2.lib' dosyalarını seçer Bu

dosyalar yine OrCAD'in LIBEDIT

programında

hazırlanırlar

ve

Şekil. 1'de verilen örneğin benzeri

semboller içerirler.

1. GİRİŞ

Tümdevre tasarımında

standart

hücre kullanımı tasarımcıya hem

kolaylık hem de zamandan tasarruf

sağlamaktadır. Bu yöntemde standart

sayısal devre blokları, genel amaçlı

olarak, önceden hazırlanıp, kullanıma

hazır bir şekilde bekletilmektedir. Bu

kütüphane elemanı hücreler, hem

şematik tasarım hem benzetim için

gerekli tanımları hem de silisyum pul

(vvafer) üzerine transfer edilecek

geometrik

desenleri

içerirler.

Kullanıcının

arzu

ettiği

işlevi

gerçekleyecek

devre

blokları,

hazırlanan bu kütüphaneden alınarak

kullanılır.

2. PC ORTAMI

Yazılım ortamı genel olarak bir serim

(layout) editörü ve ona bağlı yardımcı

programlar ile bir şematik editörden

oluşmaktadır. Ayrıca sayısal ve

analog benzetim için gerekli paket

programlar da mevcuttur. Hücre

kütüphanesinin

bu

yazılımlarla

kullanılabilmesi için gerekli dosyalar

YİTAL'de hazırlanmıştır.

Şekil.1: 3-girişli NOR (NO3) sembolü

Çizim bu semboller ile gerçekleştirilir.

Tümleştirilecek devrenin kılıf ile

bağlantısının yaılabilmesi için 'pad

hücreleri' kullanılır. Çizim bitirildikten

sonra sayısal benzetime geçilir.

Benzetim için GATESIM ya da

ORCAD kullanılabilir. GATESIM için.

şematik çizimin 'vvirelist' formatında

netlistinin alınması,

sonra bu

dosyanın

format

dönüştürücü

program (NETTRAN) ile GATESIM

tarafından kullanılacak

formata

dönüştürülmesi gerekir. Dönüştürme

programı, kütüphane için yazılan

tanım dosyalarını kullanır. Bu netlistte

her sembol bir makroya karşılık gelir.

Her makro, makro işlevini belirten

terimleri, pin isimlerini ve bağlı

oldukları düğümleri, çıkış pinlerinin

sürdükleri

yüke

göre

değişen

gecikmelerini içerir. ORCAD için yine

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 475 -

netlist oluşturmak gerekir. Fakat bu

sefer dönüştürücü programa ihtiyaç

yoktur.

YİTAL

hücrelerinin

benzetiminin

yapılabilmesi

için

'yitalsd.dsf

ile

'yitalsc2.dsf

dosyalarının hazır olması gerekir.

Benzetim

programı,

hücrelerin

işlevleri ve kullanacağı gecikmeler

için bu dosyaları kullanır. Benzetim

sonucu devre istenen işlevleri ve

gecikmeleri

sağlıyorsa

serimin

hazırlanmasına geçilebilir.

oluşur. Üçüncü bölgede ise bu iki

bölge arasındaki bağlantılar vardır.

Yİ130

2.2. Serim Tasarımı

Şematik

tasarım

tamamlandıktan

sonra 'vvirelist' formatında netlist

oluşturulur. Bu netlist NETTRAN ile

serim editör programı L-Edit'in SPR

(P&R-Place and Route) formatına

dönüştürülür. Bu dönüşüm için gerekli

dosyalar kütüphaneye özgüdür. LEdit

'yitalib4.tdb'

serim

kütüphane

dosyasını kullanır. Bu dosya her

hücrenin L-Edit ile çizilmiş serim

tanımını içerir. Serim tanımı, üretim

sürecinde maskelerin yapılmasında

kullanılan

tabakalardan

oluşur.

Şekil.2'de, daha önce sembolü

verilen 3-girişli NOR hücresinin serimi

bulunmaktadır. L-Edit'te bulunan P&R

yeteneği, şematik tasarımdan gelen

netlist ve 'yitalib4.tdb'den gelen hücre

serim bilgisi ile, istenilen tümdevrenin

seriminin,

program

tarafından

otomatik

olarak

oluşturulmasını

sağlar.

Program

hücrelerin

yerleştirilmelerini

ve

birbirleri

arasındaki bağlantıları yapar. Serimi

üç bölgeye ayırabiliriz. En dışta 'pad'

hücrelerinden

oluşan

'padframe'

denilen bölge bulunur. Kılıfla bağlantı

buradaki 'pad' hücrelerinin büyük

metal alanlarına tel bağlantısı ile

gerçekleştirilir. En içte, devrenin asıl

işlevini gerçekleyen 'core' bulunur.

'Core' standart hücre sıraları ve onlar

arasındaki bağlantı bölgelerinden

Abut

Şekil.2: 3 girişli NOR (NO3) serimi

2.3. Son kontrol

Serim tamamlandıktan sonra L-Edit'in

Extract yeteneği ile tümdevrenin

spice

netlisti

elde

edilir.

Transistörlerin

ve

diğer

devre

elemanlarının tanımlanabilmesi için

ı

yital4.ext' dosyası kullanılır. Bundan

sonra iki yöntem uygulanabilir.

İlkinde, elde edilen spice netlisti bir

spice

benzetim

programında

kullanılır. Devre hem işlevsel hem de

zamanlama açısından kontrol edilir.

Diğer bir yöntem serimden elde edilen

spice netlistini, şematikten çıkışındaki

netlist ile karşılaştırmaktır. Şematikten

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 476 -

'vvirelist'

elde

edildikten

sonra

NETTRAN

ile spice formatına

dönüştürülür. (NETTRAN diğer hücre

tanım dosyalarından farklı fakat

benzer dosyalar

kullanır).

LVS

(Layout Versus Schematic) programı

ile karşılaştırma işlemi gerçekleştirilir.

3. İŞ-İSTASYONU ORTAMI

Büyük çaplı tasarımlar için işistasyonu ortamı kullanılır. CADENCE

bu

ortamın

temel

yazılımıdır.

CADENCE'ta tasarımlar kütüphaneler

halinde tutulurlar. Bir kütüphanede

bulunan

tasarım

başka

bir

kütüphanedeki tasarımı bir alt parçası

olarak kullanabilir. YİTAL'in 3fam

CMOS standart hücre kütüphanesi de

'yital3u1' ismiyle CADENCE için

hazırlanmıştır.

Kütüphaneler

hücrelerden oluşurlar. Bunlar standart

hücre olabildikleri gibi standart

hücrelerden meydana gelen bloklar,

'full-custom' makrolar da olabilirler.

Her hücre bir görüntüler (view)

bütünüdür. Bir hücrenin serim,

şematik, sembol, verilog, abstract gibi

görüntüleri olabilir. Serim görüntüsü

maske tabakalarını belirler. Sembol

görüntüsü şematik tasarım için

kullanılır,

hücre

giriş/çıkışlarını

tanımlar. Şematik görüntü, oluştuğu

alt hücreleri ve bu hücreler arası

bağlantıları

betimler.

Verilog

görüntüsü sayısal benzetim için

kullanılır; hücre zamanlarını, giriş ve

çıkışlarını, hücrenin işlev bilgisini

içerir. Abstract görüntüsü P&R

işlemlerinde kullanılır; hücrenin serim

alanını

ve

bağlantı

noktalarını

tanımlar. Bunlardan başka bazı

görüntüler

de

bulunabilir.

Her

kütüphanenin bir teknoloji dosyası

bulunur. Bu dosyada serim tasarım

kuralları, serimden transistor ve diğer

devre elemanlarını çıkarma bilgileri ve

benzeri bir çok tanım bulunur.

3.1. Şematik Tasarım

Kütüphane oluşturulduktan sonra,

tümdevrenin

şematik

çizimi

gerçeklenir. Eğer tasarım hiyerarşik

bir yapıysa, hiyerarşik blokların her

biri için bir hücre oluşturulur. Bundan

sonra her hücrenin şematik görüntüsü

çizilir. Benzetim her hücre için tek tek

yapılabileceği gibi, bütün devre

birlikte de yapılabiiir.Sayısal benzetim

için,YİTAL'de verilog kullanılmaktadır.

VHDL, hatta tasarımcıya özel bir

benzetim programı da CADENCE

ortamına entegre edilebilir.

'celldetlne

modüle NO3 (Y.A.B.C);

input A. B C;

output Y;

specify

specparam cellarea = 7200

specparam RiseStrengthSASY

0-"1 8-3 ospecparam FallStrengthSASY = 1 0-1 7-2 0-> 0-"1 8'3 ospecparam RiseStrensthSBSY

|"

specparam FallStrengthSBSY =

0-1 7-2 Dspecparam RiseStrengthSCSY _ -t .0:2.8:3 .0:

1

specparam FallStrengthSCSY —

0:1.7:2 0:

~" 1 .

specparam max_loadSY = 2 .00:

specparam FanoutLoadSA = 0.26:

specparam FanoutLoadSB = 0.26:

specparam FanoutLoadSC = 0.26:

specparam

tA Yr = 3 0-3 7 •4 01

specparam

tA Yf = 2 0-" 8 •3 0t B Y r = 3 .0:3.7 4.0:

specparam

tB Yf = 2 .0:2.8 3.0:

specparam

specparam

tC Yr = 3 .0:3.7 4.0;

specparam

tC Yf = 2 .0:2.8 3.0;

(A-=>Y) = (tA Yr. tA YO;

(B-==> Y) = (tBYr. tB_ Yf):

(C-==> Y) = (tC_Yr. tC_ YO;

endspecify

nor(Y.A.B.C);

endmodule

'endcelldefıne

Şekil.3: NO3 verilog tanım dosyası

Benzetimin yapılabilmesi için çizimde

kullanılan her hücrenin standart hücre

kütüphanesinde Şekil.3'tekine benzer

verilog tanımı bulunmalıdır.

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 477

3.2. Serim Tasarımı

Şematik tasarım bittikten sonra netlist

çıkarılır ve

P&R gerçekleştirilir.

CADENCE P&R programı ile hücreler

gruplar

halinde

yerleştirilip,

bağlantıları yapıldıktan sonra gruplar

arası bağlantı yapılabilir. Full-custom

serımlerle standart hücre serimleri

birleştirilebilir. Serim tamamlandıktan

sonra parazitik yapılar çıkarılıp verilog

benzetiminde kullanılabilir. Böylece

narazıtık yapıların etkileri sayısal

benzetimde görülebilir. Bunlar PC

ortamına

göre

avantajlardan

bazılarıdır. İstenirse serimden devre

elemanları çıkarılabilir. Bu işlem

sonucu extracted' görüntü oluşur. Bu

görüntüde

transistörler,

diyotlar.

kapasiteler gibi devre elemanları

bulunur. Görüntünün netlisti alınıp,

spıce benzetimi yapılabilir. Bu netlist

ayrıca LVS kontrolü için de kullanılır.

Pullar YİTAL'de kesilerek kırmıklara

ayrılmış, kılıflanmış ve test edilmiştir.

Test sonuçları, bilgisayarda elde

edilen

benzetim

sonuçları

ile

uyuşmakta olup, giriş çıkış uçları

arasında ortalama 30 ns. işaret

gecikmesi ölçülmüştür.

4. SONUÇ

YİTAL'in 3um n-kuyu tek katman

polisılisyum tek katman metal CMOS

süreci için oluşturulmuş CMOS

Standart Hücre Kütüphanesi hem PC

hem de iş istasyonları ortamında

çalışır

durumdadır.

NETAŞ'a

tasarlanan iki Uygulamaya Özgü

Tümdevre için, PC ortamındaki

yazılımlar ve PC için oluşturulan

kütüphane

kullanılmıştır.

Üretilen

tümdevrelerden FRPC kodlu devre 84

giriş çıkış bağlantı pabucu ve yaklaşık

200 standart hücre içeren D-tipi ikili

(füp-flop) ağırlıklı bir veri transfer

devresidir. FRXN kodlu devre ise 61

giriş çıkış bağlantı pabucu ve yaklaşık

250 standart hücre içeren D-tipi

ikililerle oluşturulmuş, özel bir bölücü

olarak tanımlanabilir. Her iki kırmık

(chıp) yaklaşık 5.8mm x 5.8mm

boyutlarında olup p tipi silisyum pul

üzerinde

üretilmişlerdir

(Şekil.4).

Şekii.4: FRPC tümdevresinin fotoğrafı

Engin KONUR

Elektronik Y.Müh

İTÜ ('82 - M'85)

İTÜ Arş.Grv.: '82-'86

TÜBİTAK MAM: '86İ. Can ÇEVİKBAŞ

Elektonik Müh.

Boğaziçi Ü.('93)

TÜBİTAK MAM: '93-

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 478 -

CMOS SÜREÇLERİNİ VE BU SÜREÇLERLE OLUŞTURULAN

DEVRE ELEMANLARINI TEST İÇİN KULLANILAN TÜMDEVRELER

Engin KONUR

TÜBİTAK MAM YİTAL Gebze 41470 KOCAELİ

ÖZET: TÜBİTAK Marmara Araştırma

Merkezi

Yarıiletken

Teknolojisi

Araştırma

Laboratuarı

YİTAL'de

geliştirilen 3um, n-kuyu, bir katman

polisilisyum, bir katman metal CMOS

süreçleri ile, geliştirilmekte olan 1.5(jm

çift-kuyu, iki katman polisilisyum iki

katman metal CMOS süreçlerini ve bu

süreçlerle üretilen devre elemanlarını

test

etmek

amacıyla

modüler

yapılardan

oluşan

iki

tümdevre

(integrated circuit) tasarlanmış ve

üretilmiştir.

1. ÜRETİLEN TEST TÜMDEVRELERİ

İÇİN GENEL ÖZELLİKLER

Tümdevreleri oluşturan modüller, bir

test yapıları kütüphanesi oluşturacak

şekilde

tasarlanmış,

modüllerdeki

bağlantı pabuçlarının boyutları 75um x

75um ve pabuçlar arası da 75um

olarak

çizilmiştir.

Böylece

bütün

modüller, 150pm ve katları ile ifade

edilen genişlik ve yüksekliklere sahip

olmakta ve test tümdevresi geometrik

yerleşim planının (layout) hazırlanması,

değişik

boyutlarda

fayansların,

belirlenmiş bir alana yerleştirilmesi

durumuna benzer hale gelmektedir.

yapılar, eklem belverme gerilimlerinin

yanısıra,

tıkama

yönü

kaça*

akımlarının, iletim gerilimi ve iletim yonu

dirençlerinin ölçülmesini sağlarlar. Bu

amaçla, p(taban)-n(kuyu), p(taban>

n+(S/D) ve n(kuyu)-p+(S/D-source/draım

eklemleri

için

oluşturulan

test

yapılarından bir örnek,

Sekilide

verilmiştir.

p+(S/D)

n+(S/D)

HJ "

n(kuyu)

p(taban)

Şekil. 1: n(kuyu) / p+(S/D) eklemi

Şekil.1' e ait yapının akım gerilim eğrisi

Şekil.2'de verilmiştir. Üç farklı eklem

için yapılan ölçümler sonucu elde

edilen değerlerin özeti Tablo. 1'dedir.

2. TEST YAPILARI

2.1 p-n eklem testleri

CMOS tümdevre üretim süreçleri ile

oluşan çeşitli eklemlerin akım-gerilim

eğrilerinin çıkarılması için kullanılan bu

n+(S/D)/p(taban)

p+(S/D)/n(kuyu)

p(taban)/n(kuyu)

VBv

V,on

32

27

86

0.5

0.6

0.5

(V)

(V)

Tablo. 1: Eklem karakteristikleri

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 479 -

'sat

(pA/mm )

25

1.6

16

İP

CuA)

Yapı

Kontak

Direnç

[um x um]

[fi]

1.polisilisyum

1.5 x 1.5

3.5

2.polisilisyum

1.5 x 1.5

5.0

1.polisilisyum

3x3

3.5

2.polisilisyum

3x3

3.5

n+(S/D)

3x3

10

+

p (S/D)

3x3

12

Tablo.2: Kontak direnci ölçüm sonuçları

250. 0

50. 00

/d iv

-250. 0

-29. 90

VP

3.200/div

C V)

. 0000

Şekil.2: p+(S/D) / n(kuyu) I-V eğrisi

2.2 Arayüzey kontak direnci testleri

Silisyum taban malzemesi içinde veya

üzerinde oluşturulan elektriksel devre

elemanlarını birbirine bağlamak için,

YİTAL'de %1 silisyum katkılı alüminyum

kullanılmaktadır. Bu bağlantı, 1.5um

CMOS süreci için, 1.5um x 1.5um alana

sahip kontak pencereleri sayesinde

oluşturulur. Bu geçiş bölgesinde oluşan

elektriksel direncin ölçülmesi için Kelvin

direnci yapısı kullanılmıştır. Bu yapının

ve ölçüm yönteminin sembolik gösterimi

Şekil.3'te verilmiştir.

2.3 Tabaka direnci ölçme yapıları

İmplantasyon, difüzyon ve depolama

yöntemleriyle oluşturulan bölgelerin

elektriksel direnç özellikleri "tabaka

direnci" ile ifade edilebilir. Tabaka

dirençlerinin ölçülmesi için Şekil.4'de

gösterilen Van der Pauw yapısı

kullanılır. Bu yapıya şekildeki gibi (I)

akım kaynağı uygulanıp voltmetre ile

(V) gerilimi ölçülürse tabaka direnci,

Rt = — - — —

loge 2 I

şeklinde hesaplanır. İM

v

v

(3)

Ground

kontak'

Şekil.4: Van der Pauw yapısı

katman 1

Yapı

Şekil.3: Arayüzey kontak direnci. R=V/I

+

+

Bu test yapısı, n (S/D), p (S/D),

1 .polisilisyum ve 2.polisilisyum kontak

direnci için uygulanmış ve ölçülen

değerler Tablo.2' de verilmiştir.

Tabaka direnci

[Q/kare]

2600

n(kuyu)

30

n+(S/D)

+

80

p (S/D)

18

1.polisilisyum

17

2.polisilisyum

Tablo.3: Ölçülen tabaka dirençleri

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 480 -

2.4 Takılma (Latch-Up) olayı testleri

CMOS tümdevrelerde oluşan pnpn

yapılan, besleme gerilimi ile veya

parazitik

nedenlerle

tetiklenerek

tümdevrelerin bozulmalarına neden

olabilir. Birim alana yerleştirilen eleman

sayısını

artırmak

için

geometrik

yerleşim

kurallarında

yapılacak

derişiklikler

takılma

olayı

riskini

artırabilir. Test tümdevrelerinde, takılma

olayını karakterize etmek için, değişik

tasarım kuralları ile test yapıları

tasarlanmıştır.

2.5 Yüzey kaçak akımı testleri

Standart

MOS

tranzistörlerin

ve

izolasyon oksitleri altında oluşan

parazitik

tranzistörlerin

kanal

bölgelerinden;

eşik gerilimlerinden

mutlak değerce daha küçük geçit

gerilimlerinde akan akım değerlerinin

daha kolay ve güvenilir ölçümü için,

kanal genişliği (W), kanal boyu (L)

değerine oranla çok büyük tranzistörler

tasarlanmıştır.

Geçit

Oksit

Malzemesi

Kalınlığı

425 °A polisilisyum

6000 °A polisilisyum

15000°A alüminyum

Tablo.3: W/L oranı büyük

Kanal Bölgesi

VV/L oranı

2610um/3um

1860um/8um

1560um/4um

tranzistorlar

Dört faklı kontak yapısının her biri için

816 kontaklı bir zincir oluşturularak 100

mm çaplı pul (vvafer) yüzeyinde

yaklaşık

80

defa

tekrarlanmıştır.

Basamak

örtme

yapılarında

ise

minimum boyutlu metal ve polisilisyum

hatlar, 300um x 300um alanda yine

minimum boyutlarda şekillendirilmiş

silisyumdioksit üzerinde yoğun olarak

tekrarlanmaktadır.

2.7 Tranzistör testleri

Üretilecek fonksiyonel tümdevrelerin,

üretilmeden önce devre benzetim

(circuit simulation) paket programları

yardımıyla

yapılacak

analizlerinin,

üretimden sonra ölçülen sonuçlarla

uyumlu olabilmesi, devre elemanlarının

doğru modellenmesi ile mümkün

olacaktır. Bu amaçla çeşitli boyutlarda

NMOS ve PMOS tranzistörler, test

tümdevresi

içinde

tasarlanarak

üretilmişlerdir.

Çeşitli

boyutlarda

tranzistör kullanılması; hem geometrik

boyutların

parametreler

üzerindeki

etkisini modellemek hem de efektif

kanal

boyu

ve

genişliği

gibi

parametreleri daha doğru tespit etmek

için gerekli görülmüştür. Bir örnek

olarak W/L=3um/3um PMOS tranzistör

çıkış özeğrileri Şekil.5'te verilmiştir.

IDS

(uA)

-50. 00.

Bu yapılarda V GS =0V ve VDS=5V İçin

yüzey kaçak akımları 4 pA/um 'den

küçük olarak ölçülmüştür.

2.6 Süreç testleri

Kontak elemanlarının sürekliliği ile

metal hatların polisilisyum ve lokal oksit

basamaklarını örtme yeteneğini test

eden yapılar tasarlanarak, rastgele hata

yoğunluğu üzerine bir fikir edinilebilir/2/

.OOOO _

. OOOO

VDS

.5000/dlv

C V)

-5. 000

Şekil.5: 3um/3um PMOST çıkış özeğrisi

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 481 -

2.8 Evirici (inverter) gecikme testleri

Tümdevrelerdeki eviricilerin kendisi gibi

bir eviriciyi sürmesi durumunda, bu

eviricinin girişine uygulanan bir lojik

işaretin evriğinin çıkışta oluşmasına

kadar geçecek süreyi ölçmek amacıyla

51 katlı bir evirici zinciri oluşturulmuş ve

51. eviricinin çıkışı 1. eviricinin girişine

bağlanarak bir ring osilatörü meydana

getirilmiştir. Ölçme ucunun osilatör

çalışmasını etkilemesini önlemek için

bu uç bir tampon (buffer) ile dışarı

alınmaktadır. Bu yapı ile evirici

gecikmesi 1 ns. ölçülmüştür.

2.9 Standart hücre testleri

« » * p m p' i ^

«f * « » • » m m

YİTAL. standart hücre ile Uygulamaya

Özgü Tümdevre (-Application Specific

Integrated

Circuit-ASIC)

üretim

yeteneğine

sahiptir.

Bu

amaçla

hazırlanan standart hücre kütüphanesi

elemanları test tümdevresı içinde

üretilerek,

fonksiyonel

devre

tasarımından önce test edilmektedir.

2.10 Desen test yapıları

Şekil.6 Testchip mikrofotoğrafı (1995)

Litografi

olarak

adlandırılan

ve

bilgisayarda

tasarlanan

geometrik

şekillerin pul üzerine transferi olarak

kısaca tanımlayabileceğimiz süreçlerin

performansını gözlemek amacıyla 1.0u,

1.5p, 2.0u, 2.5u, 3.0u vb. gibi

boyutlarda

ve

çeşitli

şekillerde

geometrik desenler tasarlanmıştır.

KAYNAKÇA

3. SONUÇ

İM

Bullis,

Murray W.

(Editör),

Semiconductor Measurement Tech.,

Progress Report, April 1977

121 Mitchell, Michael A., Linholm Loren

W., Test Patterns NBS-28 and NBS28A: Random Fault Interconnect Step

Coverage and other structures, March

1981

Üretilen her iki test tümdevresinin

kırmık (chip) boyutları 3mm x 3mm'dir.

İki tümdevrede toplam olarak 100 farklı

test yapısı bulunmaktadır

(Şekil.6).

Üretilen pullar kesilerek kırmıklara

ayrılmış, ring osilatörü ve standart

hücreler kılıflanmıştır.

Engin KONUR

Elektronik Yük.Müh.

Lisans: İTÜ 1982

Lisansüstü: İTÜ 1985

İTÜ Arş.Grv.: '82-'86

TÜBİTAK MAM: '86-

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 482 -

CMOS GÖRÜNTÜ ALGILAMA YONGASI TASARIMI VE

GERÇEKLEŞTİRİLMESİ

Gülay YARDIM, Murat AŞKAR

TÜBİTAK Bilgi Teknolojileri ve Elektronik Araştırma Enstitüsü. 06531 ODTÜ. ANKARA

TÜBİTAK Bilgi Teknolojileri ve Elektronik Araştırma Enstitüsü. 06531 ODTÜ. ANKARA

ÖZET

Bu bildiride 2.4|j.m n-kuyulu CMOS

teknolojisi kullanılarak gerçekleştirilen bir

görüntü algılama yongasının tasarımı ve test

sonuçlan sunulmuştur. Optik algılayıcı

olarak p+/n fotodiyotlar kullanılmıştır.

Görüntü algılayıcı 16x16 fotodiyot dizilimi,

adresleme devresi, akım yükselteci ve

transempedans yükselteciden oluşmaktadır.

Görünür dalga boylarında (380-720 nm)

çalışan yonganın besleme gerilimi 5 V,

yaklaşık alanı 9 mm'dir. Prototip üretimi

sonrası

yapılan

testlerde

görüntü

algılayıcının tasarlandığı şekilde çalıştığı

gözlenmiş ve harf, rakam gibi basit şekillerin

siyah-beyaz görüntüleri elde edilmiştir.

I. GİRİŞ

Tümleşik algılayıcılar hem algılama

elemanlarını hem de elektronik devreleri

aynı tümdevre üzerinde bir araya getirdiği

için az yer kaplamakta ve gerekli donanım

miktarını azaltmaktadır /I/. Bu çalışmada

CMOS teknolojisi kullanılarak bir görüntü

algılayıcı gerçekleştirilmiştir. Geniş Çaplı

Tümdevre (VLSI) üretiminde oldukça

yoğun olarak kullanılan CMOS teknolojisi

ile gerçekleştirilen tümleşik algılayıcıların

ınauyeti çok düşük olmakta ve algılama

işlemi

bir

VLSI

ahbloğu

olarak

modellenmektedir.

CMOS teknolojisinin hammaddesi

olan silikonun ışığa karşı duyarlılığı

kullanılarak tasarlanan bu yongada optik

algılayıcı olarak CMOS'ta gerçekleştirme

kolaylığı ve devreler ile arabağlama şartları

düşünülerek

fotodiyotlar

kullanılmıştır.

CMOS teknolojisi esas olarak sayısal devre

tasarımı için geliştirilmesi sebebiyle fotodiyotun optik özellikleri ile ilgili çalışmanın

tasarımcı tarafından gerçekleştirilmesi gerekmektedir. Bu amaçla görüntü algılayıcıda

kullanılacak fotodiyotun optik özelliklen

teorik olarak hesaplanarak bir fotodiyot

modeli geliştirilmiştir.

II. FOTODİYOT MODELLEMESI

İlk olarak CMOS teknolojisinde

tasarlanabilecek

değişik

fotodiyot

topolojileri arasından n-kuyusu ile alttaştan

izole olduğu için p+/n fotodiyotun görüntü

algılayıcıda kullanılmasına karar verilmiştir.

Daha sonra

bu

fotodiyotun

optik

özelliklerini tesbit etmek amacıyla, görünür

dalgaboylarındaki spektral tepkisi hesaplanmıştır 121. Hesaplamalara göre p+/n

fotodiyotun

görünür

dalgaboylarındaki

spektral tepkisi 0.1-0.25 A/W arasında

değişmektedir ki bu miktar p+/n fotodiyotun

optik algılamada kullanılması için yeterlidir.

Ters eğilimli bir fotodiyotun aktif alanı AD,

üzerine düşen \ dalga boyundaki ışığın

şiddeti P (W/m:) ve spektral tepkisi R-A.

(A/W) olsun. Bu durumda üretilen fotoakım

miktarı

(D

eşitliği ile verilir 131. Buna göre p+/n

fotodiyot bir diyot ve akım kaynağı olarak

modellenebilir (Şekil 1). Bu model görüntü

algılayıcının simülasyonlannda kullanılmıştır.

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 483 -

X» XI XI XJ

SATUt ADRESLCAa

DEVRESİ

A

\İS

\L/ \]y

TOTODİYOT

DİZİLİMİ

aa a • a •

aaaaaa

a oa a aa

aaaaaa

aaaaaa

Şekil 1. Fotodiyot Modeli

^-s

AKıM

YÛKSELTECI

TT

TKANSCMPEDAAS

VOlCSELTTC

SÜTUN ADRESLEME

DEVRESİ

m. GÖRÜNTÜ ALGILAYICI TASARIMI

Görüntü algılayıcılar bir görüntüyü elektrik

işaretine çevirirler. Bu çalışmada tasarlanan

görüntü algılama yongası üzerine düşürülen

görüntüyü devamlı tarayarak her noktadaki

ışık şiddetiyle doğru orantılı bir analog

gerilim üretmektedir. Görüntü algılayıcı dört

bölümden oluşmaktadır:

i. Fotodiyot Dizilimi

ii. Adresleme Devresi

iii. Akım Yükselteci

iv. Transempedans Yükselteç

3.1 Görüntü Algılayıcı Çalışma Prensibi

Fotodiyot diziliminin oluşturduğu

fotoduyarlı bölge üzerine bir görüntü

düşürüldüğünde, her fotodiyot kendi üzerine

düşen ışık şiddeti ile doğru orantılı bir

fotoakım

üretir

(Şekil

2).

4x16

kodçözücülerden oluşan adresleme devresi,

yonga bacaklarına uygulanan X ve Y

adreslerine göre dizilim üzerindeki sadece

bir hücreyi aktif hale geçirir. Aktif hücre

üzerindeki fotoakım Ip, akım yükselteç

devresinde

yükseltilir.

Transempedans

devresi ise yükseltilen akımı gerilime çevirir.

Tüm hücreler sırayla tarandığında ise yonga

çıktısında görüntü bilgisi bir analog gerilim

olarak oluşur.

Yt Yİ Y2 Yi

Şekil 2. Görüntü Algılama Yongası Blok

Şeması

3.2 Fotodiyot DizilimiTasarımı

Fotodiyotların yanyana dizilmesi sonucu

oluşturulan fotoduyarlı alan 16x16 görüntü

elemanı içermektedir. Her hücrede bir p+/n

fotodiyot ve 2 nmos transistor bulunmaktadır. Şekil 3'de bir görüntü elemanı

için devre şeması verilmiştir.

GORUNTU

ELEMANI

Şekil 3. Görüntü Elemanı Devre Şeması

Fotodiyot ters eğilimli olarak çalışmakta ve

oluşan fotoakım Mı üzerinden geçmektedir.

Bu hücrenin adresi uygulandığında, M s d

transistoru

görüntü

elemanını

akım

yükselteç devresine bağlar.

3.3 Akım Yükselteci ve Transempedans

Yükselteç Tasarımı

Yongalarda

alan

çok

küçük

olduğundan, fotodiyot üzerinde oluşan

fotoakım da çok düşük olmaktadır. Bu

algılayıcıda fotodiyotlar 80,um x 80|.ım yü-

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 484 -

zey alanına sahip olacak şekilde tasarlanmıştır. Örneğin, ışık şiddetinin 0.1 W/m2

olduğu bir ortamda (oda aydınlatması),

spektral tepkisi 0.25 A/W olan bir

fotodiyotun üzerinde oluşacak fotoakım

0.16 nanoamperdir. Fotoakımı mikroamperler seviyesine yükseltmek amacıyla akım

modu bir yaklaşımla Şekil 4'deki mimari

esas alınarak akım yükselteç devresi

tasarlanmıştır. Bu devrede akım aynalarından faydalanılmıştır. Bir akım aynası

devresinde yansıtılan akım ve giriş akımı

arasındaki oran, çıkış ve giriş transistor

boyutlarının oranına eşittir /4/. Akım

yükselteci devresinde ardarda bağlanmış

akım aynaları kullanılarak fotoakım doğrusal

olarak arttırılmaktadır. Şekil 4'de verilen

devre

fotodiyot

diziliminin

çıktısına

bağlanmaktadır.

i

ı

işlemsel

^"""s's-»*^^

out

yükseltec

v

ref

.,,

V

ÜUİ

^0^"^^'

,

1 V

Şekil 5. Transempedans Yükselteç

Vout seçilen hücre üzerindeki

aşağıdaki eşitlikle bağlıdır:

fotoakıma

(2)

ref

IV. TEST SONUÇLARI

Simülasyonları yapılan ve serimi

hazırlanan yonganın prototipleri yurtdışında

2.4|.ım CMOS teknolojisiyle üretilmiştir.

Yonga Şekil 6'daki görüntüleme sistemi

kullanılarak test edilmiştir.

mır KATCAC

O

/

Bu devrede akım kazancı ortamdaki ışık

şiddetine göre S0 ve Sİ girişleri (Şekil 2)

kullanılarak xlO, xl00, xl000 veya x 10000

olarak ayarlanabilir.

Yükseltilen akım işlemsel yükselteç,

gerilim referansı ve yonga dışına yerleştirilen

bir direncin oluşturduğu transempedans

yükselteç aracılığıyla gerilime çevrilir (Şekil

5). Gerilim referansının işlevi akım aynalarının çıkış transistörlerini sabit akım

bölgesinde tutmaktır.

®|oo

a

o

\ . .

—*N,

^

•••II A/>

Şekil 4. Akım Yükselteç Devresi

I

o

üi

=

aaac

Şekil 6. Görüntü Algılama Yongası Test

Düzeneği

Bu

düzenekte

yonga

bir

fotoğraf

makinasında film yerine yerleştirilerek

algılanacak objenin fotoduyarlı alan üzerine

düşmesi sağlanmıştır. PIC 16C71 mikrodenetleyici ve TSC232'den oluşan bir devreyle

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 485 -

adres üretme, analog-sayısal çevirim ve

sayısal görüntü verisinin bilgisayara aktanmı

gerçekleştirilmiştir. Fotometre ortamdaki

ışık şiddetini ölçmek amacıyla kullanılmıştır.

Şekil 7'de görüntü algılama yongasıyla elde

edilmiş bazı görüntüler verilmiştir. Fotoğraf

makinası merceğinin ışık şiddetini azaltnası

sebebiyle testler sırasında akım yükselteci

x 10000 modunda çalıştırılmıştır. Testler

esnasında her görüntü elemanı için örnekleme zamanı 100 us'dir.

Bu

yonga

tümleşik

optik

algılayıcıların CMOS teknolojisi kullanılarak

gerçekleştirilebileceğini göstermiştir. CMOS

teknolojisi

kullanılarak tasarlanan

bu

görüntü algılayıcı hiç bir özel işlem

gerektirmediği için maliyeti sıradan sayısal

yongalar kadar düşüktür. Ayrıca aynı yonga

üzerinde

algılama

ve

işaret

işleme

gerçekleştirilmektedir.

Kaynakça

İM M.R. Haskard. I.C. May. Analog VLSI Design

nMOS and CMOS. Prentice Hail. Ne\vYork. 1988.

IIIG. Yardım. Iınplementation of Integrated Optical

Sensors on a CMOS VLSI Chip. MS Thesis.

Elcctrical and Electronics Eng. Dep. Middle East

Technical University. January 1995.

13/ S.M. Sze. Senıiconductor Devices Physics and

Technology. John Wiley&Sons. Singapore. 1985.

/4/ R.Grcgorian. G.C.Temes. Analog MOS

Integrated Circuits for Signal Processing. John

Wiley&Sons. Ne\v York. 1986.

Özgeçmişler

Şekil 7. Görüntü Algılayıcıyla Oluşturulan

Görüntü Örnekleri

V. SONUÇ

Şekil 7'de görüldüğü gibi görüntü

algılayıcı basit şekilleri, sayı veya rakamları

rahatlıkla algılamaktadır. Daha karışık

şekillerin algılanamaması ve kenar çizgilerinin köşeli olması çözünürlüğün düşük

olmasından

kaynaklanmaktadır.

Kenar

üzerinde yer alan bazı noktaların gri olarak

algılanmasının sebebi ise o fotodiyotun hem

beyaz hem de siyah yüzeyden yansıyan ışığa

maruz kalmasıdır. Tarama periodu teorik

olarak 1 (.ıs kadar düşebilmesine rağmen

yongaya ulaşan ışık şiddetinin az olması

sebebiyle daha uzun periodlarda daha kaliteli

görüntü elde edilmiştir.

Gülay YARDIM 1971 yılında Ankara'da doğdu.

Lisans ve yüksek lisans eğitimlerini ODTÜ Elektrik

ve Elektronik Mühendisliği Bölümü'nde 1992 ve

1995 yıllarında tamamladı. 1992-1995 yılları

arasında ODTÜ Elektrik ve Elektronik Mühendisliği Bölümü Elektronik Anabilim Dalı'na bağlı

olarak araştırma görevlisi olarak çalıştı. Halen

TÜBİTAK Bilgi Teknolojileri ve Elektronik

Araştırma Enstitüsü'nde Elektronik Sistemler ve

Tümdevre Tasarım Grubu'nda araştırıcı olarak

çalışmaktadır.

Murat AŞKAR 1952 yılında Ankara'da doğdu.

Lisans, yüksek lisans ve doktora derecelerini ODTÜ

Elektrik ve Elektronik Mühendisliği bölümünden

sırasıyla 1974. 1976 ve 1981 yıllarında alan Dr.

Aşkar. yine aynı üniversitede 1984 yılında doçent ve

1991 yılında profesör oldu. Dr. Aşkar. 1987-1988

ders yılında misafir öğretim üyesi olarak University

of California'da bulundu. ODTÜ'de öğretim üyeliği

görevlerine ek olarak TÜBİTAK Ankara Elektronik

Araştırma ve Geliştirme Enstitüsü Müdürlüğü. TRT

Stüdyolar Dairesi Başkanlığı görevlerinde bulunan

Dr. Aşkar endüstriyel projelerde araştırmacı ve

yönetici olarak çalıştı. Çok sayıda yayımlanmış

makalesi bulunan Dr. Aşkar halen TÜBİTAK Bilgi

Teknolojileri ve Elektronik Araştırma Enstitüsü

Müdürlüğünü yürütmektedir.

ELEKTRİK MÜHENDİSLİĞİ 6. ULUSAL KONGRESİ

- 486 -

CMOS SÜRECİ İÇİN ÇİFT KATMAN POÜSİÜSYUM KAPASİTE

YAPILARININ OPTİMİZASYONU

Barbaros Şekerkıran

TÜBİTAK MAM YİTAL Gebze 41470 KOCAELİ

ÖZET

TÜBİTAK-MAM-YİTAL

bünyesinde

3um tek polisilisyum (poli) ve tek metal

katmanlı n-kuyu CMOS

sürecine

yüksek birim alan kapasitesine sahip,

düşük kaçaklı çift katmanlı polisilisyum

kapasite yapılarını eklemek üzere

denemeler

yapılmış

ve

uygun

özelliklere sahip yapılar elde edilmiştir.

Çift

poli

kapasitelerini

içeren

tümdevreler

YİTAL 'de başarıyla

tasarlanmış ve gerçekleştirilmiştir.

1)ÇİFT POLİ KAPASİTE YAPISI

Günümüzde CMOS analog ve sayısal

devrelerin tümleştirilmesi birçok yeni

uygulamaya

olanak

sağlamaktadır.

Birçok sayısal VLSI süreci, uygun

özelliklere sahip kapasite yapıları

eklenerek sayısal devrelerin yanında

analog blokların da gerçeklenebileceği

hale getirilebilir. Kapasitenin özelliklen

yalıtkan tabakanın ve bu tabakanın

altında ve üstünde bulunan iletken

tabakaların

yapısal

ve

elektiksel

özelliklerine bağlıdır. Ayrıca polisilisyum

tabakalar arasındaki kapasitenin, bu

tabakaların diğer iletkenlerle

olan

kaçak kapasitelerine kıyasla

büyük

olması beklenir. Sürece eklenen işlem

adımlarının, sayısının az. sürelerinin

kısa, ısıl bütçelerinin küçük, olmasının

yanında güvenilir ve tekrar edilir olması

istenir.

Çift poli kapasite yapısının kesiti Şekil.

1 de görülmektedir. Tabana olan kaçak

kapasitenin küçük olması için kapasite

daima ince oksit yerine kalın alan oksiti

üzerine

yerleştirilir.

Katkılanıp

şekillendirilen birinci poli katmanı

oksitlenir ve ikinci poli tabakası

depolanır. İki polisilisyum katmanının

arasındaki ince oksit, kapasitenin

yalıtkanıdır. Ne var ki polisilisyumun

oksitlenmesinden elde edilen SiO2 in

elektriksel

özellikleri

monokristal

silisyumun

oksitlenmesinden

elde

edilen oksitlerinkine erişemez. Ayrıca

oksitlenen polisilisyum yüzeyi pürüzlü

bir hal alır ve sivri noktalarda

yoğunlaşan elektriksel alan şiddetinden

dolayı bu bölgelerde tünelleme akımları

yüksek olur.

Bu nedenlerle yüksek

birim alan kapasiteleri verebilecek

olsalar bile, 500 A° den ince poli

oksitleri kullanılmaz /1,2/. Elektrotları

oluşturan polisilisyum katmanlarının

dirençlerinin

düşük

yani

katkı

yoğunluklarının yüksek olması istenir.

Bunun iki nedeni vardır; 1) Bir

yarıiletken olan polisilisyumun yüzeyleri

uygulanan

gerilime

bağlı

olarak