6.6. SPICE Simülasyonunda Kullanılmaya Yönelik Bir Analog

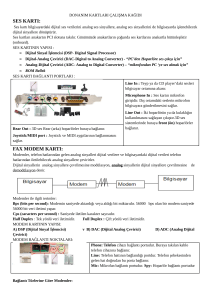

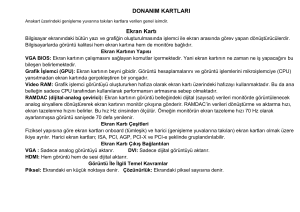

advertisement

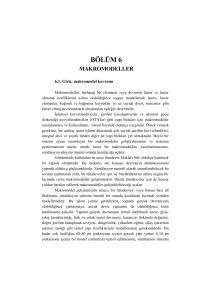

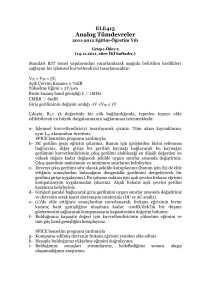

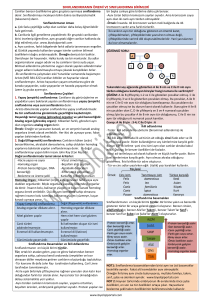

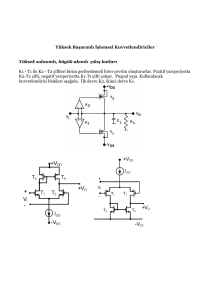

6. 35 6.6. SPICE Simülasyonunda Kullanılmaya Yönelik Bir Analog Çarpma Devresi Makromodeli 6.6.1. Analog çarpma devresi Analog çarpma devreleri, giriú gerilimlerinin çarpımıyla orantılı çıkıú gerilimi veren düzenlerdir ve aradaki iliúki (6.17) V O = K.V X .V Y úeklindedir. K büyüklü÷ü çarpma devresinin kazanç sabiti olarak isimlendirilir. VO büyüklü÷ü çıkıú gerilimini, VX ve VY büyüklükleri de giriú gerilimlerini göstermektedir. Analog çarpma devreleri, tümdevre tekni÷inde kazancı gerilimle kontrol edilen kuvvetlendirici, faz kilitlemeli çevrim, faz karúılaútırıcı, modülatör, demodülatör, frekans ço÷altıcı gibi uygulamalara iliúkin düzeneklerin gerçekleútirilmesinde yaygın olarak kullanılmaktadır . Literatürde iúlemsel kuvvetlendirici, iúlemsel geçiú iletkenli÷i kuvvetlendiricisi (OTA), akım taúıyıcı (CCII) gibi yaygın olarak kullanılan yapıların makromodelleri bulunmasına karúılık, analog çarpma devresi makromodellerine rastlanmamaktadır. Bu bölümde, çeúitli biçimlerdeki devre topolojileri ile gerçekleútirilen analog çarpma devrelerinin SPICE programıyla simülasyonunda kullanılmaya yönelik bir makromodel gerçekleútirilmiú, makromodel yardımıyla elde edilen analog çarpma devresi karakteristikleri, eleman modeli yardımıyla SPICE simülasyonundan elde edilen sonuçlarla ve deneysel sonuçlarla karúılaútırılarak kurulan modelin do÷rulu÷u gösterilmiútir. 6.6.2. Temel analog çarpma devresi yapıları Analog çarpma devrelerinin temel hücresi, gerek bipolar tümdevre gerekse MOS tümdevre tekni÷inde, emetör (veya kaynak) ba÷lamalı fark kuvvetlendiricisidir. Dört bölgeli analog çarpma devresi gerçekleútirmek üzere Gilbert hücresi olarak isimlendirilen altı tranzistorlu bir yapı kullanılır. Bu yapıda iki fark kuvvetlendiricisinin giriúleri paralel, çıkıúları ise çapraz olarak ba÷lanmıútır. Fark kuvvetlendiricilerin ortak kuyruk akımları ise bir di÷er fark 6. 36 +VCC RC1 'I RC2 (VY1-VY2)3 + VO - (VY1-VY2)2 VX1 (VY1-VY2)1 T5 T6 T3 T4 VX2 VY1 T1 T2 VX1-VX2 -(VY1-VY2)1 VY2 RY -(VY1-VY2)2 IEE/2 IEE/2 -(VY1-VY2)3 -VEE ùekil-6.25.a) Analog çarpma devresi, b) tipik giriú-çıkıú karakteristi÷i (RY=0 için). +VCC +VC RC1 RC2 + VO - T9 T10 T5 T6 T3 T4 VX1 VY1 T7 T1 T8 IX T2 VY2 RY RX VX2 IX IY IY -VEE ùekil-6.26. Lineerleútirilmiú analog çarpma devresi. kuvvetlendiricisinin çıkıú akımlarıyla sa÷lanmaktadır. Bu úekilde oluúturulan devrenin bipolar tekni÷inde ne úekilde gerçekleútirildi÷i ùekil-6.25a’da görülmektedir. ùekil-6.25a’da yer alan ve bipolar tranzistorlarla gerçekleútirilmiú olan devrede çıkıú akımının giriú gerilimlerine ba÷ımlılı÷ı 6. 37 'I I EE .tanh> (V X 1 V X 2 ) / VT @ tanh> (VY 1 VY 2 ) / VT @ (6.18) biçimindedir. Uygun kutuplama ile tranzistorların doymaya girmemesi sa÷lanarak yüksek bir çalıúma hızı elde edilebilir. Giriúlerden birinin geriliminin, (VY1-VY2) parametre alınmasıyla elde edilen giriú-çıkıú karakteristikleri ùekil-6.25b’de verilmiútir. (6.18) ba÷ıntısından ve ùekil-6.25b’den fark edilebilece÷i gibi, devre küçük genlikli iúaretler için lineer çarpma iúlemini yerine getirmektedir. Büyük genlikli iúaretler söz konusu oldu÷unda, lineerleútirilmiú bir yapıdan yararlanılır. Bu yapı ùekil-6.26’da verilmiútir. ùekil-6.26’daki devrenin çıkıú gerilimini giriú gerilimlerine ba÷layan ifade VO 2.R L (V X 1 V X 2 ).(VY 1 VY 2 ) I X R X .RY (6.19) biçimindedir. 6.6.3. Önerilen Makromodel Bu çalıúmada önerilen analog çarpma devresi makromodeli ùekil6.27’de görülmektedir. Genel amaçlı olarak hazırlanmıú olan bu model bipolar ve MOS tekni÷inde gerçekleútirilen tüm yapılar için kullanılabilmektedir. ùekil-6.27’deki makromodeldeki elemanların modelledikleri ve karúı düútükleri büyüklükler aúa÷ıda belirtilmiútir: X giriúi: R1 dirençleri X giriúi fark iúaret giriú direncini, C2 fark iúaret giriú kapasitesini, R2 X giriúi ortak iúaret direncini, C1 ortak iúaret giriú kapasitesini, IBX X giriúi kutuplama akımını, VOX X giriúine iliúkin dengesizlik gerilimini, VCMX ortak iúaret davranıúını temsil etmektedir. IA, R5, C5 hücresi birim kazançlı bir kat oluúturur; bu kat X giriúine iliúkin frekans e÷risinin baskın kutbunu belirler. IA, R5 and C5 büyüklükleri 6. 38 V5 ID1 VYY=VB/2 + VYY + VYY IBX VA = V1-V2 VOX V1 R1 R2 +VX1 C1 D1 R7 R1 R2 R5 V3 R3 R4 R3 R4 C3 V4 VCMY R6 IBY D8 R8 D3 ID3 ID1 D4 ID4 VB C4 +VY2 + VZZ + VZZ - IBY C3 V6 VZZ=VS/2 C5 IA VOY +VY1 VA IBX V2 VCMX IB1 VS = V5-V6 D2 R7 C1 D7 R8 VXX=VA/2 C2 +VX2 IB2 ID2 + VXX + VXX - IB VB = V3-V4 C6 + VZZ + VZZ - D6 ID5 ID2 D5 ID6 +VO1 IO1 = ID3 +ID5 IO1 C7 IO2 = ID4 +ID6 + VC - IO2 C7 R10 R10 +VO2 ùekil-6.27. Geliútirilen analog çarpma devresi makromodeli IA R5 C5 g mx .(V1 V2 ) 1 g mx 1 2. S . f 3dBx . R5 (6.20) (6.21) (6.22) ba÷ıntıları ile verilmektedir.. Burada g mx IX VT oda sıcaklı÷ında VT=kT/q=26mV olarak tanımlanmaktadır. (6.23) 6. 39 VXX , D7, D8, R8, IB1 hücresi T7-T8 çiftine iliúkin lineer olmayan davranıúı modeller. R8 direnci geçiú bölgesi geniúli÷ini belirler, IB1 = 2IX bu hücrenin ortak kutuplama akımıdır. Y giriúi: Benzer bir yapı Y giriúi için öngörülmüútür. R3 dirençleri Y giriúi fark iúaret giriú direncini, C4 fark iúaret giriú kapasitesini, R4 Y giriúi ortak iúaret direncini, C1 ortak iúaret giriú kapasitesini, IBY Y giriúi kutuplama akımını, VOY Y giriúine iliúkin dengesizlik gerilimini, VCMY ortak iúaret davranıúını modellemektedir. IB, R6, C6, birim kazançlı bir hücredir ve Y giriúine iliúkin frekans e÷risinin f3dBY baskın kutbunu belirler. IB, R6, C6 büyüklükleri IB g mY .(V3 V4 ) (6.24) R6 1 g mY (6.25) C6 1 2.S . f 3dBY . R6 (6.26) úeklinde tanımlanırlar, burada g mY IY VT (6.27) ba÷ıntısıyla verilmektedir. VYY, D1, D2, R7, IB2 hücresi T1-T2 çiftine iliúkin lineer olmayan davranıúı modeller. R7 geçiú bölgesi geniúli÷ini belirler, IB2 bu hücrenin ortak kutuplama akımıdır. VZZ, D3, D4, ID1 hücresi T3-T4 çiftine iliúkin lineer olmayan davranıúı modeller. ID1 bu hücrenin ortak kutuplama akımını göstermektedir. VZZ, D5, D6, ID2 elemanlarından oluúan benzer bir hücre T5-T6 çiftinin lineer olmayan daranıúını modeller, ID2 akımı bu hücrenin ortak kutuplama akımıdır. Çıkıú hücresi: IO1, IO2, C7, R10, VC hücresi çıkıú hücresini oluúturur. IO1 ve IO2 iki kolun çıkıú akımlarıdır. R10 dirençleri kol çıkıú dirençlerini, C7 kapasiteleri de kol çıkıú kapasitelerini vermektedir. VC çıkıú do÷ru gerilimi seviyesini modeller. 6. 40 6.6.4. Simülasyon sonuçları (a) (b) ùekil-6.28. Gilbert hücresi için gerçek devre ve makromodel yardımıyla elde edilen giriú- çıkıú karakteristikleri. a) Eleman modeli, b) makromodel. Geliútirilen analog çarpma devresi makromodeli ile XR2208 (XR2228) tipi bir analog çarpma devresinin (ùekil-6.26) simülasyonları yapılmıú ve tipik karakteristikleri çıkartılmıútır. Çarpma devresi XR B101 npn dizi tranzistorları ile kurulmuú ve simülasyonlarda bu tranzistorların parametreleri 6. 41 kullanılmıútır.Simülasyonlarda besleme gerilimleri VCC = 12V ve -VEE = - 12V, kutuplama akımları da IX = IY = 0.5mA olarak alınmıútır. ùekil-6.28’de RX =RY = 0 için gerçek devre (eleman modeli) ve makromodel için elde edilen simülasyon sonuçları görülmektedir. E÷riler çıkartılırken giriúlerden birine uygulanan do÷ru gerilim (VY1-VY2) parametre olarak alınmıú, bu do÷ru gerilim -50mV ile +50mV de÷erleri arasında 25mV aralıklarla de÷iútirilmiú, bu giriúe uygulanan her gerilim de÷eri için di÷er giriúe bir tarama gerilimi uygulanmıútır. ùekil-6.28’den fark edilebilece÷i gibi, devre küçük gerilim de÷erleri için do÷rusal özellik göstermekte, büyük gerilim de÷erlerinde tanh karakteristi÷i nedeniyle bozulma ortaya çıkmaktadır. ùekil-6.28b’den görülebilece÷i gibi, makromodelden elde edilen sonuçlar gerçek devre sonuçlarıyla uyumludur. RX = RY =10k:’luk dirençlerle lineerleútirilen devre için aynı yoldan hareket edilerek giriú-çıkıú karakteristi÷i çıkartılmıú ve ùekil-6.29’da verilmiútir. Fark edilebilece÷i gibi, lineerleútirme direncinin katılmasıyla giriú geriliminin de÷iúim aralı÷ı -2.5V ile +2.5V sınırlarına yükselmiútir. Bu da gerçek devre üzerinde yapılan ölçümlerden bilinen bir sonuçtur. ùekilden görülebilece÷i gibi, eleman modeli ile yapılan simülasyonların sonuçları, makromodel kullanılarak yapılan simülasyonların sonuçlarıyla uyumludur. Lineerleútirilmiú devrede sabit VY gerilim de÷erleri için vo/vx geçiú fonksiyonunun frekans cevabı, eleman modeli ve makromodel kullanılarak SPICE simülasyonuyla çıkartılmıú, elde edilen sonuçlar ùekil-6.30’da verilmiútir. ùekiller çizilirken yatay eksen VX1 büyüklü÷üne göre ölçeklenmiútir. Gerçek giriú geriliminin (VX1-VX2) oldu÷una dikkat edilmelidir. Aynı analog çarpma devresiyle kurulan bir frekans ikileyici devresi için eleman modeli ve makromodel kullanılarak simülasyonla elde edilen dalga úekilleri de ùekil-6.31’de verilmiútir. Giriúlere 1V genlikli ve 1MHz frekanslı sinüs iúaretleri uygulanmıútır. 6. 42 3V 1V -1V -3V (a) 3V 1V -1V -3V (b) ùekil-6.29.Lineerleútirilmiú analog çarpma devresi için eleman modeli ve makromodel ile elde edilen giriú- çıkıú karakteristikleri. a) eleman modeli b) makromodel 6. 43 3V 1V (a) 3V 1V (b) ùekil-6.30. Lineerleútirilmiú analog çarpma devresi için bir giriúe uygulanan farklı do÷ru gerilim de÷erleri için makromodel yardımıyla elde edilen frekans e÷rileri. 6. 44 (a) (b) ùekil-6.31. Analog çarpma devresiyle kurulan bir frekans ikileyici devresi için simülasyonla elde edilen dalga úekilleri. a) eleman modeli b)makromodel. Giriúlere 1V genlikli ve 1MHz frekanslı sinüs iúaretleri uygulanmıútır. 6. 45 ùekil-6.28, 6.29, 6.30 ve 6.31 de verilen sonuçlar, makromodel ve eleman modeli ile elde edilen sonuçların birbiriyle uyumlu olduklarını ortaya koymaktadır. Her iki model için gereken simülasyon süreleri, ùekil-6.28, 6.29, 6.30 ve 6.31 için kullanılan test devreleri için karúılaútırılmıú, elde edilen sonuçlar Tablo-6.9’da verilmiútir. Elde edilen do÷rulu÷un yüksek olmasına karúılık, makromodel yardımıyla gerçekleútirilen simülasyonlar önemli ölçüde kısalmaktadır. Tablo-6.9. Simülasyon sürelerinin karúılaútırılması. Model/Analiz DC (sn) AC (sn) Transient (sn) Eleman Modeli Makromodel 45 140 180 33 115 120 6.6.5. Sonuç Bu çalıúmada, analog çarpma devrelerinin simülasyonunda kullanılmak üzere genel bir makromodel önerilmiútir. Önerilen makromodel bipolar ve MOS teknolojisi ile gerçekleútirilen bütün analog çarpma devrelerine uygulanabilir. ùekil-6.26’daki lineerleútirilmiú bipolar analog çarpma devresi örnek olarak alınırsa, bu devre akım kayna÷ı düzenlerinin dıúında 10 tranzistor, dolayısıyla 20 pn jonsiyonu içermektedir. Gerçek devre simülasyonunda her bir jonksiyon için dinamik davranıúın (kapasitelerin) da modellendi÷i dikkate alınırsa, sadece bu devrenin davranıúının incelenmesi için SPICE programının bu tranzistorlara iliúkin modellerden kaynaklanan lineer olmayan cebirsel ve lineer olmayan diferensiyel denklemleri çözmesi gerekece÷i açıktır. Geliútirilen makromodel, aynı davranıúı 8 pn jonksiyonu ve bunlara ek olarak gelen lineer devreler yardımıyla modellemektedir. pn jonksiyonları sadece statik lineer olmayan davranıúı modellemekte, bütün dinamik davranıú lineer elemanlarla temsil edilmektedir. Bu da simülasyon süresini önemli derecede kısaltmaktadır. Bu açıdan bakıldı÷ında, önerilen modelin, analog çarpma devrelerinin yaygın 6. 46 olarak ve çok sayıda kullanıldı÷ı haberleúme sistemlerinin SPICE simülasyonunda önemli derecede yarar sa÷layaca÷ı ve simülasyon süresini önemli derecede kısaltaca÷ı söylenebilir. KAYNAKLAR [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] A.B. Grebene, Bipolar and MOS analog integrated circuit design, John Wiley, 1984. P.R. Gray, R.G. Meyer, Analysis and design of analog integrated circuits, John Wiley, 1993. H. Kuntman, Analog tümdevre tasarımı, Sistem yayınları, østanbul, 1992. H. Kuntman, øleri analog tümdevre tasarımı: Analog devreler, (Endüstri Semineri Notu), øTÜ øleri Elektronik Teknolojileri Araútırma Geliútirme Vakfı (ETA), østanbul,1994 H. Kuntman, Analog MOS tümdevre tekni÷i, øTÜ Kütüphanesi, Sayı:1587, østanbul,1997 G.R. Boyle, B.M. Cohn, D.O. Pederson and J.E.Solomon, macromodeling of integrated circuit operational amplifiers, IEEE, JSSC, 9, 353-363, 1974. R.V. Peic, Simple and accurate nonlinear macromodel for operational amplifiers, IEEE, JSSC, 26, 896-899, 1991. H. Kuntman, Simple and accurate nonlinear OTA macromodel for simulation of CMOS OTA-C filters, Int. Journal of Electronics, 77, 993-1006, 1994. N. Tarım, B. Yenen and H. Kuntman, Simple and accurate nonlinear current conveyor macromodel, Melecon 96, Proceedings of 8th Mediterranean Electrotechnical Conference, 447-450, Bari, Italy, May 13-16, 1996. N. Tarım, B. Yenen and H. Kuntman, Simple and accurate nonlinear current conveyor macromodel for simulútion of active filters using CCIIs, Int. Journal of Circuit Theory and Application, 26, 27-38, 1998. H. H. Kuntman: Simple and accurate nonlinear analogue multipiler macromodel, Melecon'98: 9th Mediterranean Electrotechnical Conference, Vol.1, pp 585-589, May 18-20, Tel Aviv, Israel, 1998. H. H. Kuntman: Endüstriyel Elektronik, Birsen Yayınevi, østanbul, 1998.