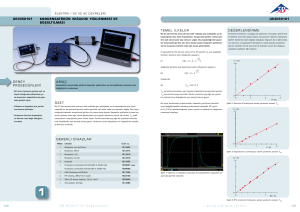

DENEY 1: RC DEVRESİ GEÇİCİ HAL DURUMU Deneyin Amaçları

advertisement

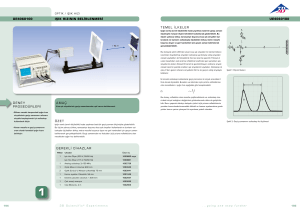

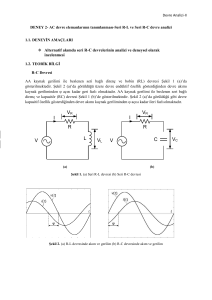

DENEY 1: RC DEVRESİ GEÇİCİ HAL DURUMU Deneyin Amaçları RC devresini geçici hal durumunu incelemek Kondansatörün geçici hal eğrilerini (şarj ve deşarj) elde etmek, Zaman sabitini kavramını gerçek devrede görmek Deney Malzemeleri İşaret Üreteci (Fonksiyon Jeneratörü), Osiloskop, 10kΩ Direnç, 1uF Kondansatör, Breadboard, Bağlantı Probları (Altı çizili malzemeleri öğrenciler kendisi getirecektir. Diğer malzemeler laboratuvarda verilecektir.) Teorik Bilgi Kondansatör (Capacitance-Capacitor): Elektrik yüklerini depolayabilen pasif devre elemanıdır. Kapasitör veya Sığa olarak da isimlendirilir. Birimi Farad(F) dır. C ile gösterilir. Bobin (Inductance): Enerjiyi manyetik alan olarak depolayan devre elemanıdır. Endüktans ya da indüktans olarak da isimlendirilir. Birimi Henry(H)’dir. L ile gösterilir. Zaman Sabiti (τ): RC ve RL devrelerinde, gerilimlerdeki ve akımlardaki belirli değişimler için gereken zamanın bir ölçüsüdür. Anahtarlama olduktan sonra geçen süre, zaman sabitin 5 katı (5τ) ise, akımlar ve gerilimler son değerine ulaşır. 1. RC Devresi Bir RC devresinde zaman sabiti, eşdeğer kapasitörün uçlarındaki Thevenin direnci ve eşdeğer kapasitörün çarpımıdır. τ=RC R + VR + VC - Vin C Şekil 1. Seri RC Devresi Kapasitörün başlangıç enerjisi sıfır olan Şekil 1’deki RC devresi Kirşof kanunlarına göre analiz edilecek olursa kapasitör üzerindeki Vc geriliminin zamana bağlı denklemi şu şekilde olur: t≥0 Bu denklemin zamana göre grafiği Şekil 2’deki gibi olur. Burada kapasitör üzerindeki V gerilimi Vin kaynak gerilimine eşittir. Bu grafik seri RC devresinde kapasitörün dolma eğrisidir. Şekil 2. Seri RC devresinde Kapasitörün Dolma Eğrisi Şekil 1’deki devrede Vin kaynak gerilimi kısa devre yapılacak olursa kapasitör üzerindeki gerilim zamana göre denklemi şu şekilde olur, Bu denklemde V0 kaynak geriliminin kısa devre yapıldığı anda kapasitör üzerindeki depolanan gerilimdir. Kapasitör üzerindeki gerilim R üzerinde harcanır. Kapasitörün boşalma eğrisi Şekil 3 de ki gibi olur. Şekil 3. Kapasitörün Boşalma Eğrisi 2. RL Devresi Bir RL devresinde zaman sabiti eşdeğer bobinin uçlarındaki direnç toplamına bölümüdür. Zaman sabiti ise τ= dir. KMU Elektrik Elektronik Mühendisliği Devre Analizi II Laboratuvarı Deney 1 2 Şekil 4. Seri RL Devresi Bobinin ilk akımı sıfır olan Şekil 4’deki RL devresi Kirşof kanunlarına göre analiz edilecek olursa bobinden akan akım IL zamana bağlı denklemi şu şekilde olur; RL devresinin zaman sabiti τ= dir. Bu denklemin grafiği aşağıdaki gibidir. Bu grafik bobin üzerinde akımın depolanma eğrisidir. Şekil 5. Bobinin Üzerinden Akan Akım Değişimi Şekil 1 deki RL devresinde V kaynağı kısa devre yapılırsa ve bobinin depoladığı akım I0 olarak kabul edilirse bobinin üzerindeki akım zamana bağlı akım denklemi şu şekilde olur. Bu denklemin zaman göre grafiği şöyledir, Şekil 6. Bobin Üzerinde depolanan Akımın Boşalma Eğrisi KMU Elektrik Elektronik Mühendisliği Devre Analizi II Laboratuvarı Deney 1 3 ÖN HAZIRLIK SORULARI 1) RC devresine aşağıda grafiği verilen Vin gerilimi uygulanıyor. Kapasitör geriliminin dolma ve boşalma eğrilerini çiziniz, denklemlerini elde ediniz. R=10k + VR - + VC - Vin C=1µF Şekil 7. Vin Kaynak Gerilimi 2) Yukarıdaki devreyi Multisim, Proteus vb bir program üzerinde kurunuz. Kaynak olarak Pulse_Voltage kullanınız. Kaynağın periyodunu 100 ms, pulse width 50 ms olarak ayarlayınız. Kapasitörün dolma ve boşalma eğrilerini osiloskop ile elde ediniz. Program üzerindeki devrenizi ve osiloskop grafiğinin çıktısını veriniz ve devrenin zaman sabitini grafik üzerinde gösteriniz. KMU Elektrik Elektronik Mühendisliği Devre Analizi II Laboratuvarı Deney 1 4 DENEYSEL ÇALIŞMA VE SONUÇLAR Ön hazırlık çalışmasında verilen devreyi breadboard üzerine kurunuz. Vin kaynak gerilimini fonksiyon üreteci(AG1022) kullanarak devreye uygulayınız. Fonksiyon üretecinde sinyal tipi olarak Pulse seçiniz ve periyodunu 100 ms, duty cyle 50 ms olarak ayarlayınız. Fonksiyon üreteci ve osiloskop arasında uygun prop bağlantısını sağlayınız. Fonksiyon prop girişi üzerindeki on/off tuşu ile sinyal çıkışını aktif ediniz. Osiloskobun ekranında grafik düzgün değilse horizontal ve vertical bölümlerinde bulunan tuşlar ile X ve Y eksenlerinin aralığını ayarlayınız. Osiloskop ekranındaki grafiği inceleyiniz ve zaman sabitini hesaplayınız. Grafiği çiziniz. Zaman sabiti τ = Osiloskop Ekranı X ekseni aralığı (X div) Y ekseni aralığı (Y div) KMU Elektrik Elektronik Mühendisliği Devre Analizi II Laboratuvarı Deney 1 5