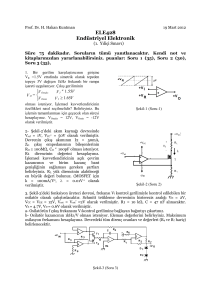

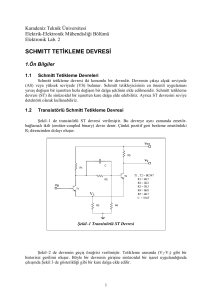

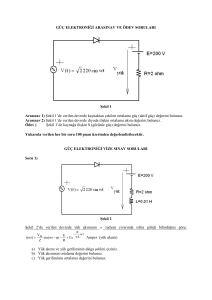

SAYISAL TASARIM Derin

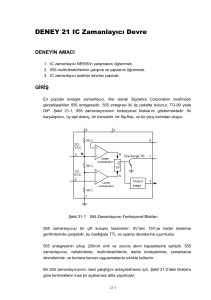

advertisement